AVDD_DDR0

R1201 |

|

| 1K 1% |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| |

R1202 |

| 1K 1% | C1201 |

|

| 0.1uF C1202 |

|

| 1000pF | ||

|

|

|

|

| |||||||

|

|

|

| ||||||||

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

CLose to DDR3

AVDD_DDR0

R1204 |

|

|

| 1%1K |

|

|

|

|

|

|

| +1.5V_DDR |

| AVDD_DDR0 |

|

|

|

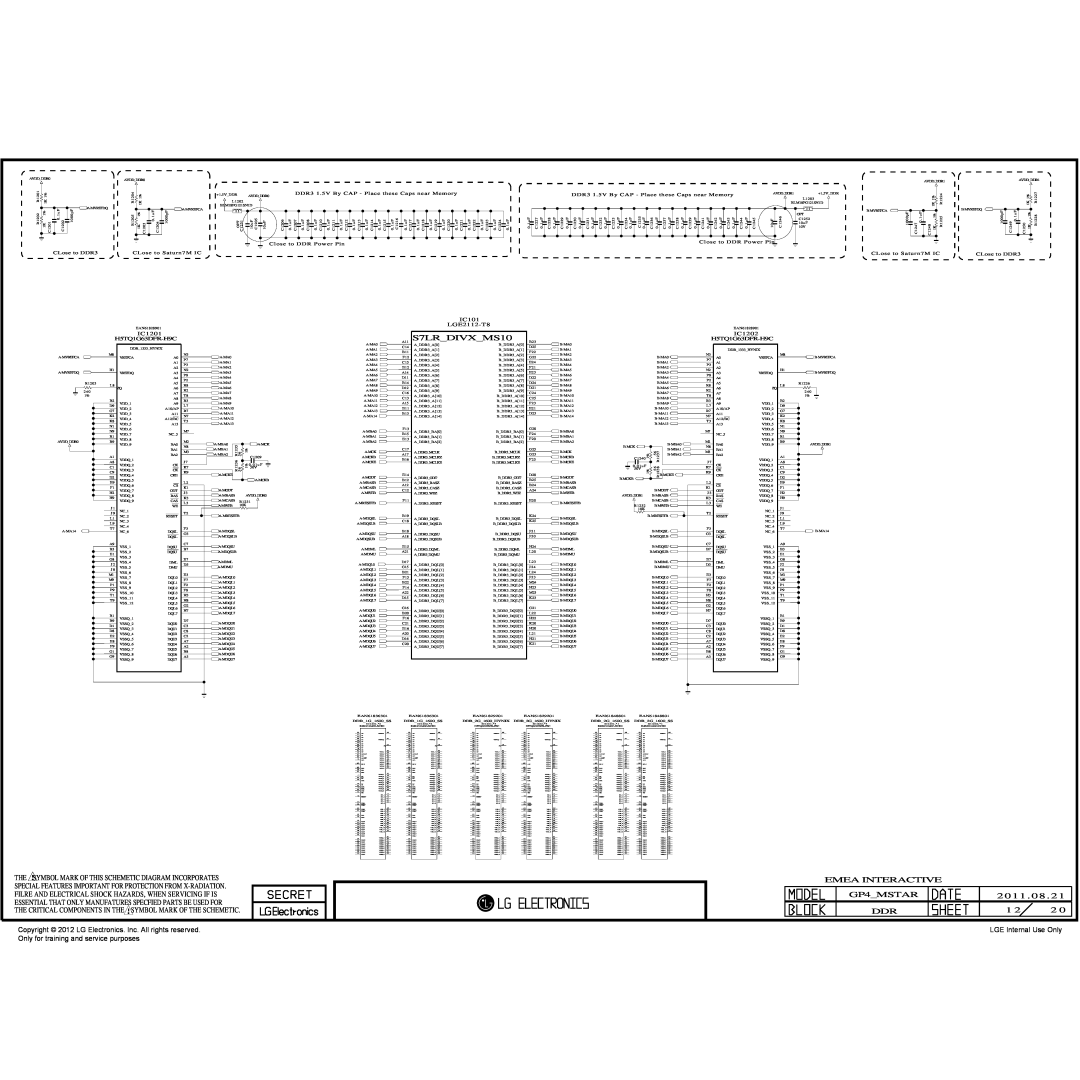

| DDR3 1.5V By CAP - Place these Caps near Memory |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L1202 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| BLM18PG121SN1D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

R1205 |

|

| 1K 1% | C1203 |

|

| 0.1uF C1204 |

|

| 1000pF |

|

|

| OPT C1251 |

|

| 10uF C1205 |

|

| 10uF | C1206 |

|

| 0.1uF | C1207 |

|

| 0.1uF C1208 |

|

| 0.1uF C1210 |

|

| 0.1uF C1211 |

|

| 0.1uF C1212 |

|

| 0.1uF C1213 |

|

| 0.1uF C1214 |

|

| 0.1uF C1215 |

|

| 0.1uF C1216 |

|

| 0.1uF C1217 |

|

| 0.1uF C1218 |

|

| 0.1uF C1219 |

|

| 0.1uF C1220 |

|

| 0.1uF | C1221 |

|

| 0.1uF | C1222 |

|

| 0.1uF | C1223 |

|

| 0.1uF | C1224 |

|

| 0.1uF | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Close to DDR Power Pin

CLose to Saturn7M IC

|

|

|

|

|

|

| DDR3 1.5V By CAP - Place these Caps near Memory |

|

|

|

| AVDD_DDR1 |

|

|

|

| +1.5V_DDR | ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| L1203 |

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| BLM18PG121SN1D |

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

1.0uF | C1227 | 1.0uF | C1228 | 1.0uF | C1229 | 1.0uF | C1230 1.0uF | C1231 1.0uF | C1232 1.0uF | C1233 1.0uF | C1234 1.0uF | C1235 1.0uF | C1236 1.0uF | C1237 1.0uF | C1238 1.0uF | C1239 1.0uF | C1241 1.0uF | C1242 1.0uF | C1243 1.0uF | C1244 | 1.0uF | C1245 | 10uF | C1246 | OPT | ||||||

10V | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C1252 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 10uF | |||||

Close to DDR Power Pin

AVDD_DDR1

|

|

|

|

|

|

| 1K 1% |

|

| R1224 | |||

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 1000pF |

|

| C1247 0.1uF |

|

| C1248 | 1K 1% |

|

|

| R1225 | |

|

|

|

|

|

|

|

| ||||||

|

|

|

| ||||||||||

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLose to Saturn7M IC

AVDD_DDR1

|

|

|

|

|

|

| 1K 1% |

|

|

| R1227 | |||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 1000pF |

|

| C1249 0.1uF |

|

| C1250 | 1K 1% |

|

|

| R1228 | ||

|

|

|

|

|

|

|

| |||||||

|

|

|

| |||||||||||

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLose to DDR3

EAN61828901 |

IC1201 |

IC101

A11 | S7LR_DIVX_MS10 |

B23 |

EAN61828901

IC1202

|

| DDR_1333_HYNIX |

|

|

|

M8 |

|

| N3 | ||

| VREFCA | A0 | P7 | ||

|

|

| A1 | ||

|

|

| P3 | ||

|

|

| A2 |

| |

| H1 |

| N2 | ||

|

|

| |||

![]()

![]()

![]()

![]()

![]()

A_DDR3_A[0] | B_DDR3_A[0] |

|

|

|

|

| |

C14 |

|

| D25 | ||||

A_DDR3_A[1] | B_DDR3_A[1] |

|

|

|

|

| |

B11 |

|

| F22 | ||||

A_DDR3_A[2] | B_DDR3_A[2] |

|

|

|

| ||

F12 |

|

| G22 | ||||

A_DDR3_A[3] | B_DDR3_A[3] |

|

|

|

|

| |

C15 |

|

| E24 | ||||

A_DDR3_A[4] | B_DDR3_A[4] |

|

|

|

| ||

E12 |

|

| F21 | ||||

A_DDR3_A[5] | B_DDR3_A[5] |

|

|

|

| ||

N3

P7

P3

N2

| DDR_1333_HYNIX |

A0 | VREFCA |

A1 |

|

A2 |

|

M8

H1

|

|

|

| VREFDQ | A3 | P8 | |||||

|

|

|

|

|

|

|

| A4 |

|

| |

|

|

|

|

|

|

|

|

| P2 | ||

|

|

| R1203 |

|

|

| A5 |

|

| ||

|

|

| L8 |

| |||||||

|

|

|

|

|

|

|

| R8 | |||

|

|

| 240 |

|

| ZQ | A6 |

| |||

|

|

|

|

|

|

| A7 |

| R2 | ||

|

|

| 1% |

|

|

|

|

| T8 | ||

|

|

|

|

|

|

| A8 |

|

| ||

|

|

|

|

|

|

|

|

|

| ||

![]()

![]()

![]()

![]()

![]()

A14 |

|

| E23 | ||||||

A_DDR3_A[6] | B_DDR3_A[6] |

|

|

|

|

|

|

| |

D11 |

|

| D22 | ||||||

A_DDR3_A[7] | B_DDR3_A[7] |

|

|

|

|

|

| ||

B14 |

|

| D24 | ||||||

A_DDR3_A[8] | B_DDR3_A[8] |

|

|

|

|

|

| ||

D12 |

|

| D21 | ||||||

A_DDR3_A[9] | B_DDR3_A[9] |

|

|

|

|

|

| ||

C16 |

|

| C24 | ||||||

A_DDR3_A[10] | B_DDR3_A[10] |

|

|

|

|

|

| ||

C13 |

|

| C25 | ||||||

P8

P2

R8

R2

T8

A3 | VREFDQ |

A4 |

|

A5 |

|

A6 | ZQ |

A7 |

|

A8 |

|

L8

R1226

240

1%

|

|

|

|

|

| B2 |

|

|

|

|

|

|

|

|

|

|

|

| R3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDD_1 |

|

|

|

|

| A9 |

|

|

| |||||||

|

|

|

|

|

| D9 |

|

|

|

|

|

|

|

|

|

|

|

| L7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDD_2 | A10/AP |

|

|

| ||||||||||||

|

|

|

|

|

| G7 |

|

|

|

|

|

|

|

|

|

|

|

| R7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDD_3 |

|

|

| A11 |

|

|

| |||||||||

|

|

|

|

|

| K2 |

|

|

|

|

|

|

|

|

|

|

|

| N7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDD_4 | A12/BC |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| T3 |

|

|

| ||||||||||

|

|

|

|

|

| K8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VDD_5 |

|

|

| A13 |

|

|

| |||||||||

|

|

|

|

|

| N1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDD_6 |

|

|

|

|

|

|

|

|

|

|

|

| M7 |

|

|

|

|

|

|

|

|

| N9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VDD_7 |

|

| NC_5 |

|

|

|

| |||||||||

|

|

|

|

|

| R1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

AVDD_DDR0 |

|

|

|

|

|

|

| VDD_8 |

|

|

|

|

|

|

|

|

|

|

|

| M2 |

|

|

| |||

| R9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

| VDD_9 |

|

|

| BA0 |

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| BA1 |

| N8 |

|

|

| |||||||

|

|

|

|

|

| A1 |

|

|

| BA2 |

|

|

|

| M3 |

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_1 |

|

|

|

|

|

|

|

|

|

|

|

| J 7 |

|

|

|

|

|

|

|

|

| A8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_2 |

|

|

|

| CK |

|

|

|

| |||||||

|

|

|

|

|

| C1 |

|

|

|

|

|

|

|

|

|

|

|

| K7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_3 |

|

|

|

| CK |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| K9 |

|

|

| ||||||

|

|

|

|

|

| C9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_4 |

|

| CKE |

|

|

| ||||||||||

|

|

|

|

|

| D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| E9 |

|

|

|

|

|

|

|

|

|

|

|

| L2 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_6 |

|

|

|

|

| CS |

|

|

|

|

|

|

| |||

|

|

|

|

|

| F1 |

|

|

|

|

|

|

|

|

|

|

|

| K1 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_7 |

|

| ODT |

|

|

| ||||||||||

|

|

|

|

|

| H2 |

|

|

|

|

|

|

|

|

|

|

|

| J 3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_8 |

|

|

| RAS |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

| H9 |

|

|

|

|

|

|

|

|

|

|

|

| K3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VDDQ_9 |

|

|

| CAS |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L3 |

|

|

| ||||

|

|

|

|

|

| J 1 |

|

|

|

| WE |

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| NC_1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| J 9 |

|

|

|

|

|

|

|

|

|

|

|

| T2 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| NC_2 |

| RESET |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

| L1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| NC_3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| NC_4 |

|

|

|

|

|

|

|

|

|

|

|

| F3 |

|

|

|

|

|

| T7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

| NC_6 |

|

| DQSL |

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DQSL |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| A9 |

|

|

|

|

|

|

|

|

|

|

|

| C7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_1 |

|

| DQSU |

|

|

| ||||||||||

|

|

|

|

|

| B3 |

|

|

|

|

|

|

|

|

|

|

|

| B7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_2 |

|

| DQSU |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

| E1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_3 |

|

|

|

|

|

|

|

|

|

|

|

| E7 |

|

|

|

|

|

|

|

|

| G8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VSS_4 |

|

| DML |

|

|

| ||||||||||

|

|

|

|

|

| J 2 |

|

|

|

|

|

|

|

|

|

|

|

| D3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_5 |

|

| DMU |

|

|

| ||||||||||

|

|

|

|

|

| J 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_6 |

|

|

|

|

|

|

|

|

|

|

|

| E3 |

|

|

|

|

|

|

|

|

| M1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VSS_7 |

|

| DQL0 |

|

|

| ||||||||||

|

|

|

|

|

| M9 |

|

|

|

|

|

|

|

|

|

|

|

| F7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_8 |

|

| DQL1 |

|

|

| ||||||||||

|

|

|

|

|

| P1 |

|

|

|

|

|

|

|

|

|

|

|

| F2 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_9 |

|

| DQL2 |

|

|

| ||||||||||

|

|

|

|

|

| P9 |

|

|

|

|

|

|

|

|

|

|

|

| F8 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_10 |

|

| DQL3 |

|

|

| ||||||||||

|

|

|

|

|

| T1 |

|

|

|

|

|

|

|

|

|

|

|

| H3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_11 |

|

| DQL4 |

|

|

| ||||||||||

|

|

|

|

|

| T9 |

|

|

|

|

|

|

|

|

|

|

|

| H8 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSS_12 |

|

| DQL5 |

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DQL6 |

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| H7 |

|

|

|

|

|

|

|

|

| B1 |

|

| DQL7 |

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_1 |

|

|

|

|

|

|

|

|

|

|

|

| D7 |

|

|

|

|

|

|

|

|

| B9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_2 |

|

| DQU0 |

|

|

| ||||||||||

|

|

|

|

|

| D1 |

|

|

|

|

|

|

|

|

|

|

|

| C3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_3 |

|

| DQU1 |

|

|

| ||||||||||

|

|

|

|

|

| D8 |

|

|

|

|

|

|

|

|

|

|

|

| C8 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_4 |

|

| DQU2 |

|

|

| ||||||||||

|

|

|

|

|

| E2 |

|

|

|

|

|

|

|

|

|

|

|

| C2 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_5 |

|

| DQU3 |

|

|

| ||||||||||

|

|

|

|

|

| E8 |

|

|

|

|

|

|

|

|

|

|

|

| A7 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_6 |

|

| DQU4 |

|

|

| ||||||||||

|

|

|

|

|

| F9 |

|

|

|

|

|

|

|

|

|

|

|

| A2 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_7 |

|

| DQU5 |

|

|

| ||||||||||

|

|

|

|

|

| G1 |

|

|

|

|

|

|

|

|

|

|

|

| B8 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_8 |

|

| DQU6 |

|

|

| ||||||||||

|

|

|

|

|

| G9 |

|

|

|

|

|

|

|

|

|

|

|

| A3 |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VSSQ_9 |

|

| DQU7 |

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

![]() A-MA10

A-MA10

![]() A-MA11

A-MA11

![]() A-MA12

A-MA12

![]() A-MA13

A-MA13

| R1235 | 56 |

|

|

| |||

| 1% |

|

|

|

| |||

|

|

|

|

|

|

|

| |

|

| R1236 |

|

| C1209 | |||

|

|

|

|

|

|

|

| |

|

| 56 | 1% | 0 . 0 1 u F |

| |||

|

|

|

|

|

| |||

|

|

|

|

| 50V | |||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| ||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

A_DDR3_A[11] | B_DDR3_A[11] |

|

|

|

|

|

|

|

|

| |

A15 |

| F23 | |||||||||

A_DDR3_A[12] | B_DDR3_A[12] |

|

|

|

|

|

|

|

|

| |

E11 |

| E21 | |||||||||

A_DDR3_A[13] | B_DDR3_A[13] |

|

|

|

|

|

|

|

|

| |

B13 |

| D23 | |||||||||

A_DDR3_A[14] | B_DDR3_A[14] |

|

|

|

|

|

|

|

|

| |

F13 |

| G20 | |||||||||

A_DDR3_BA[0] | B_DDR3_BA[0] |

|

|

|

|

|

|

|

|

| |

B15 |

| F24 | |||||||||

A_DDR3_BA[1] | B_DDR3_BA[1] |

|

|

|

|

|

|

|

|

| |

E13 |

| F20 | |||||||||

A_DDR3_BA[2] | B_DDR3_BA[2] |

|

|

|

|

|

|

|

|

| |

C17 |

| G25 | |||||||||

A_DDR3_MCLK | B_DDR3_MCLK |

|

|

|

|

|

|

|

|

| |

A17 |

| G23 | |||||||||

A_DDR3_MCLKZ | B_DDR3_MCLKZ |

|

|

|

|

|

|

|

|

| |

B16 |

| F25 | |||||||||

A_DDR3_MCLKE | B_DDR3_MCLKE |

|

|

|

|

|

|

|

|

| |

E14 |

| D20 | |||||||||

A_DDR3_ODT | B_DDR3_ODT |

|

|

|

|

|

|

|

|

| |

B12 |

| B25 | |||||||||

A_DDR3_RASZ | B_DDR3_RASZ |

|

|

|

|

|

|

|

|

| |

A12 |

| B24 | |||||||||

A_DDR3_CASZ | B_DDR3_CASZ |

|

|

|

|

|

|

|

|

| |

C12 |

| A24 | |||||||||

A_DDR3_WEZ | B_DDR3_WEZ |

|

|

|

|

|

|

|

|

| |

F11 |

| E20 | |||||||||

A_DDR3_RESET | B_DDR3_RESET |

|

|

|

|

|

|

|

|

| |

B19 |

| K24 | |||||||||

A_DDR3_DQSL | B_DDR3_DQSL |

|

|

|

|

|

|

|

|

| |

C18 |

| K25 | |||||||||

A_DDR3_DQSLB | B_DDR3_DQSLB |

|

|

|

|

|

|

|

|

| |

B18 |

| J 2 1 | |||||||||

A_DDR3_DQSU | B_DDR3_DQSU |

|

|

|

|

|

|

|

|

| |

A18 |

| J 2 0 | |||||||||

A_DDR3_DQSUB | B_DDR3_DQSUB |

|

|

|

|

|

|

|

|

| |

E15 |

| H24 | |||||||||

A_DDR3_DQML | B_DDR3_DQML |

|

|

|

|

|

|

|

|

| |

A21 |

| L20 | |||||||||

A_DDR3_DQMU | B_DDR3_DQMU |

|

|

|

|

|

|

|

|

| |

D17 |

| L23 | |||||||||

A_DDR3_DQL[0] | B_DDR3_DQL[0] |

|

|

|

|

|

|

|

|

| |

G15 |

| J 2 4 | |||||||||

A_DDR3_DQL[1] | B_DDR3_DQL[1] |

|

|

|

|

|

|

|

|

| |

B21 |

| L24 | |||||||||

A_DDR3_DQL[2] | B_DDR3_DQL[2] |

|

|

|

|

|

|

|

|

| |

F15 |

| J 2 3 | |||||||||

A_DDR3_DQL[3] | B_DDR3_DQL[3] |

|

|

|

|

|

|

|

|

| |

B22 |

| M24 | |||||||||

A_DDR3_DQL[4] | B_DDR3_DQL[4] |

|

|

|

|

|

|

|

|

| |

F14 |

| H23 | |||||||||

A_DDR3_DQL[5] | B_DDR3_DQL[5] |

|

|

|

|

|

|

|

|

| |

A22 |

| M23 | |||||||||

A_DDR3_DQL[6] | B_DDR3_DQL[6] |

|

|

|

|

|

|

|

|

| |

D15 |

| K23 | |||||||||

A_DDR3_DQL[7] | B_DDR3_DQL[7] |

|

|

|

|

|

|

|

|

| |

G16 |

| G21 | |||||||||

A_DDR3_DQU[0] | B_DDR3_DQU[0] |

|

|

|

|

|

|

|

|

| |

B20 |

| L22 | |||||||||

A_DDR3_DQU[1] | B_DDR3_DQU[1] |

|

|

|

|

|

|

|

|

| |

F16 |

| H22 | |||||||||

A_DDR3_DQU[2] | B_DDR3_DQU[2] |

|

|

|

|

|

|

|

|

| |

C21 |

| K20 | |||||||||

A_DDR3_DQU[3] | B_DDR3_DQU[3] |

|

|

|

|

|

|

|

|

| |

E16 |

| H20 | |||||||||

A_DDR3_DQU[4] | B_DDR3_DQU[4] |

|

|

|

|

|

|

|

|

| |

A20 |

| L21 | |||||||||

A_DDR3_DQU[5] | B_DDR3_DQU[5] |

|

|

|

|

|

|

|

|

| |

D16 |

| H21 | |||||||||

A_DDR3_DQU[6] | B_DDR3_DQU[6] |

|

|

|

|

|

|

|

|

| |

C20 |

| K21 | |||||||||

A_DDR3_DQU[7] | B_DDR3_DQU[7] |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

| R1237 |

| ||

|

|

|

|

|

|

|

| 1% | 56 |

| ||||

|

|

| C1240 |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 . 0 1 u F |

|

| 56 | R1238 |

|

|

| |||||

|

|

| 50V | 1% |

| B | ||||||||

|

|

|

| |||||||||||

|

|

|

|

|

|

|

| |||||||

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

| |||||

AVDD_DDR1 |

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

| R1232 |

|

| |||||||||

|

|

|

| 10K |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||||

R3

L7

R7

N7

T3

M7

M2

N8

M3

J 7 K7 K9

L2

K1

J 3 K3 L3

T2

F3

G3

C7

B7

E7

D3

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

A9 | VDD_1 | ||||||||

A10/AP | VDD_2 | ||||||||

A11 |

|

| VDD_3 | ||||||

A12/BC |

| VDD_4 | |||||||

A13 | VDD_5 | ||||||||

|

|

|

|

|

|

|

|

| VDD_6 |

NC_5 | VDD_7 | ||||||||

|

|

|

|

|

|

|

|

| VDD_8 |

BA0 | VDD_9 | ||||||||

BA1 |

| ||||||||

BA2 |

| ||||||||

|

|

|

|

|

|

|

|

| VDDQ_1 |

CK | VDDQ_2 | ||||||||

CK |

|

|

|

|

|

| VDDQ_3 | ||

CKE | VDDQ_4 | ||||||||

|

|

|

|

|

|

|

|

| VDDQ_5 |

CS |

|

|

|

|

|

| VDDQ_6 | ||

ODT | VDDQ_7 | ||||||||

RAS |

|

|

|

| VDDQ_8 | ||||

CAS |

|

|

|

| VDDQ_9 | ||||

WE |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| NC_1 |

RESET |

| NC_2 | |||||||

|

|

|

|

|

|

|

|

| NC_3 |

|

|

|

|

|

|

|

|

| NC_4 |

DQSL | NC_6 | ||||||||

DQSL |

|

|

| ||||||

DQSU | VSS_1 | ||||||||

DQSU |

| VSS_2 | |||||||

|

|

|

|

|

|

|

|

| VSS_3 |

DML | VSS_4 | ||||||||

DMU | VSS_5 | ||||||||

|

|

|

|

|

|

|

|

| VSS_6 |

DQL0 | VSS_7 | ||||||||

DQL1 | VSS_8 | ||||||||

DQL2 | VSS_9 | ||||||||

DQL3 | VSS_10 | ||||||||

DQL4 | VSS_11 | ||||||||

DQL5 | VSS_12 | ||||||||

DQL6 |

| ||||||||

DQL7 |

| ||||||||

|

|

|

|

|

|

|

|

| VSSQ_1 |

DQU0 | VSSQ_2 | ||||||||

DQU1 | VSSQ_3 | ||||||||

DQU2 | VSSQ_4 | ||||||||

DQU3 | VSSQ_5 | ||||||||

DQU4 | VSSQ_6 | ||||||||

DQU5 | VSSQ_7 | ||||||||

DQU6 | VSSQ_8 | ||||||||

DQU7 | VSSQ_9 | ||||||||

B2

D9

G7

K2

K8

N1

N9

R1

R9

AVDD_DDR1

A1

A8

C1

C9

D2

E9

F1

H2

H9

J 1

J 9

L1

L9

T7

A9

B3

E1

G8

J 2 J 8 M1 M9 P1 P9 T1 T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

EAN61836301 | EAN61836301 | EAN61829201 | EAN61829201 | EAN61848801 | EAN61848801 |

DDR_1G_1600_SS | DDR_1G_1600_SS | DDR_2G_1600_HYNIX | DDR_2G_1600_HYNIX | DDR_2G_1600_SS | DDR_2G_1600_SS |

N3 | A0 | VREFCA | |

P7 | |||

P3 | A1 |

| |

N2 | A2 | VREFDQ | |

P8 | A3 | ||

P2 | A4 |

| |

R8 | A5 | ZQ | |

R2 | A6 | ||

T8 | A7 |

| |

R3 | A8 | VDD_1 | |

L7 | A9 | ||

R7 | A10/AP | VDD_2 | |

N7 | A11 | VDD_3 | |

T3 | A12/BC | VDD_4 | |

| A13 | VDD_5 | |

M7 |

| VDD_6 | |

| NC_5 | VDD_7 | |

M2 |

| VDD_8 | |

N8 | BA0 | VDD_9 | |

M3 | BA1 |

| |

J 7 | BA2 | VDDQ_1 | |

| |||

K7 | CK | VDDQ_2 | |

K9 | CK | VDDQ_3 | |

| CKE | VDDQ_4 | |

L2 |

| VDDQ_5 | |

K1 | CS | VDDQ_6 | |

J 3 | ODT | VDDQ_7 | |

K3 | RAS | VDDQ_8 | |

L3 | CAS | VDDQ_9 | |

T2 | WE | NC_1 | |

| |||

| RESET | NC_2 | |

|

| NC_3 | |

F3 |

| NC_4 | |

G3 | DQSL | NC_6 | |

C7 | DQSL | VSS_1 | |

DQSU | |||

B7 | |||

| DQSU | VSS_2 | |

E7 |

| VSS_3 | |

D3 | DML | VSS_4 | |

| DMU | VSS_5 | |

E3 |

| VSS_6 | |

F7 | DQL0 | VSS_7 | |

F2 | DQL1 | VSS_8 | |

F8 | DQL2 | VSS_9 | |

H3 | DQL3 | VSS_10 | |

H8 | DQL4 | VSS_11 | |

G2 | DQL5 | VSS_12 | |

H7 | DQL6 |

| |

D7 | DQL7 | VSSQ_1 | |

| |||

C3 | DQU0 | VSSQ_2 | |

C8 | DQU1 | VSSQ_3 | |

C2 | DQU2 | VSSQ_4 | |

A7 | DQU3 | VSSQ_5 | |

A2 | DQU4 | VSSQ_6 | |

B8 | DQU5 | VSSQ_7 | |

A3 | DQU6 | VSSQ_8 | |

| DQU7 | VSSQ_9 | |

|

|

|

M8 | N3 | A0 | VREFCA | |

| P7 | |||

| P3 | A1 |

| |

H1 | N2 | A2 | VREFDQ | |

| P8 | A3 | ||

| P2 | A4 |

| |

L8 | R8 | A5 | ZQ | |

| R2 | A6 | ||

| T8 | A7 |

| |

B2 | R3 | A8 | VDD_1 | |

D9 | L7 | A9 | ||

G7 | R7 | A10/AP | VDD_2 | |

K2 | N7 | A11 | VDD_3 | |

K8 | T3 | A12/BC | VDD_4 | |

N1 |

| A13 | VDD_5 | |

N9 | M7 |

| VDD_6 | |

R1 |

| NC_5 | VDD_7 | |

R9 | M2 |

| VDD_8 | |

| N8 | BA0 | VDD_9 | |

| M3 | BA1 |

| |

A1 |

| BA2 | VDDQ_1 | |

A8 | J 7 |

| ||

C1 | K7 | CK | VDDQ_2 | |

C9 | K9 | CK | VDDQ_3 | |

D2 |

| CKE | VDDQ_4 | |

E9 | L2 |

| VDDQ_5 | |

F1 | K1 | CS | VDDQ_6 | |

H2 | J 3 | ODT | VDDQ_7 | |

H9 | K3 | RAS | VDDQ_8 | |

| L3 | CAS | VDDQ_9 | |

J 1 |

| WE | NC_1 | |

J 9 | T2 |

| ||

L1 |

| RESET | NC_2 | |

L9 |

|

| NC_3 | |

T7 | F3 |

| NC_4 | |

| G3 | DQSL | NC_6 | |

A9 | C7 | DQSL | VSS_1 | |

DQSU | ||||

B3 | B7 | |||

E1 |

| DQSU | VSS_2 | |

G8 | E7 |

| VSS_3 | |

J 2 | D3 | DML | VSS_4 | |

J 8 |

| DMU | VSS_5 | |

M1 | E3 |

| VSS_6 | |

M9 | F7 | DQL0 | VSS_7 | |

P1 | F2 | DQL1 | VSS_8 | |

P9 | F8 | DQL2 | VSS_9 | |

T1 | H3 | DQL3 | VSS_10 | |

T9 | H8 | DQL4 | VSS_11 | |

| G2 | DQL5 | VSS_12 | |

| H7 | DQL6 |

| |

B1 |

| DQL7 | VSSQ_1 | |

B9 | D7 |

| ||

D1 | C3 | DQU0 | VSSQ_2 | |

D8 | C8 | DQU1 | VSSQ_3 | |

E2 | C2 | DQU2 | VSSQ_4 | |

E8 | A7 | DQU3 | VSSQ_5 | |

F9 | A2 | DQU4 | VSSQ_6 | |

G1 | B8 | DQU5 | VSSQ_7 | |

G9 | A3 | DQU6 | VSSQ_8 | |

|

| DQU7 | VSSQ_9 | |

|

|

|

|

M8 | N3 | A0 | VREFCA | M8 |

| N3 | A0 | VREFCA |

| P7 |

|

| P7 | ||||

| P3 | A1 |

|

|

| P3 | A1 |

|

H1 | N2 | A2 | VREFDQ | H1 |

| N2 | A2 | VREFDQ |

| P8 | A3 |

|

| P8 | A3 | ||

| P2 | A4 |

|

|

| P2 | A4 |

|

L8 | R8 | A5 | ZQ | L8 |

| R8 | A5 | ZQ |

| R2 | A6 |

|

| R2 | A6 | ||

| T8 | A7 |

|

|

| T8 | A7 |

|

B2 | R3 | A8 | VDD_1 | B2 |

| R3 | A8 | VDD_1 |

D9 | L7 | A9 | D9 |

| L7 | A9 | ||

G7 | R7 | A10/AP | VDD_2 | G7 |

| R7 | A10/AP | VDD_2 |

K2 | N7 | A11 | VDD_3 | K2 |

| N7 | A11 | VDD_3 |

K8 | T3 | A12/BC | VDD_4 | K8 |

| T3 | A12/BC | VDD_4 |

N1 |

| A13 | VDD_5 | N1 |

|

| A13 | VDD_5 |

N9 | M7 |

| VDD_6 | N9 |

| M7 |

| VDD_6 |

R1 |

| A15 | VDD_7 | R1 |

|

| A15 | VDD_7 |

R9 | M2 |

| VDD_8 | R9 |

| M2 |

| VDD_8 |

| N8 | BA0 | VDD_9 |

|

| N8 | BA0 | VDD_9 |

| M3 | BA1 |

|

|

| M3 | BA1 |

|

A1 |

| BA2 | VDDQ_1 | A1 |

|

| BA2 | VDDQ_1 |

A8 | J 7 |

| A8 |

| J 7 |

| ||

C1 | K7 | CK | VDDQ_2 | C1 |

| K7 | CK | VDDQ_2 |

C9 | K9 | CK | VDDQ_3 | C9 |

| K9 | CK | VDDQ_3 |

D2 |

| CKE | VDDQ_4 | D2 |

|

| CKE | VDDQ_4 |

E9 | L2 |

| VDDQ_5 | E9 |

| L2 |

| VDDQ_5 |

F1 | K1 | CS | VDDQ_6 | F1 |

| K1 | CS | VDDQ_6 |

H2 | J 3 | ODT | VDDQ_7 | H2 |

| J 3 | ODT | VDDQ_7 |

H9 | K3 | RAS | VDDQ_8 | H9 |

| K3 | RAS | VDDQ_8 |

| L3 | CAS | VDDQ_9 |

|

| L3 | CAS | VDDQ_9 |

J 1 |

| WE | NC_1 | J 1 |

|

| WE | NC_1 |

J 9 | T2 |

| J 9 |

| T2 |

| ||

L1 |

| RESET | NC_2 | L1 |

|

| RESET | NC_2 |

L9 |

|

| NC_3 | L9 |

|

|

| NC_3 |

T7 | F3 |

| NC_4 | T7 |

| F3 |

| NC_4 |

| G3 | DQSL | NC_6 |

|

| G3 | DQSL | NC_6 |

A9 | C7 | DQSL | VSS_1 | A9 |

| C7 | DQSL | VSS_1 |

DQSU |

| DQSU | ||||||

B3 | B7 | B3 |

| B7 | ||||

E1 |

| DQSU | VSS_2 | E1 |

|

| DQSU | VSS_2 |

G8 | E7 |

| VSS_3 | G8 |

| E7 |

| VSS_3 |

J 2 | D3 | DML | VSS_4 | J 2 |

| D3 | DML | VSS_4 |

J 8 |

| DMU | VSS_5 | J 8 |

|

| DMU | VSS_5 |

M1 | E3 |

| VSS_6 | M1 |

| E3 |

| VSS_6 |

M9 | F7 | DQL0 | VSS_7 | M9 |

| F7 | DQL0 | VSS_7 |

P1 | F2 | DQL1 | VSS_8 | P1 |

| F2 | DQL1 | VSS_8 |

P9 | F8 | DQL2 | VSS_9 | P9 |

| F8 | DQL2 | VSS_9 |

T1 | H3 | DQL3 | VSS_10 | T1 |

| H3 | DQL3 | VSS_10 |

T9 | H8 | DQL4 | VSS_11 | T9 |

| H8 | DQL4 | VSS_11 |

| G2 | DQL5 | VSS_12 |

|

| G2 | DQL5 | VSS_12 |

| H7 | DQL6 |

|

|

| H7 | DQL6 |

|

B1 |

| DQL7 | VSSQ_1 | B1 |

|

| DQL7 | VSSQ_1 |

B9 | D7 |

| B9 |

| D7 |

| ||

D1 | C3 | DQU0 | VSSQ_2 | D1 |

| C3 | DQU0 | VSSQ_2 |

D8 | C8 | DQU1 | VSSQ_3 | D8 |

| C8 | DQU1 | VSSQ_3 |

E2 | C2 | DQU2 | VSSQ_4 | E2 |

| C2 | DQU2 | VSSQ_4 |

E8 | A7 | DQU3 | VSSQ_5 | E8 |

| A7 | DQU3 | VSSQ_5 |

F9 | A2 | DQU4 | VSSQ_6 | F9 |

| A2 | DQU4 | VSSQ_6 |

G1 | B8 | DQU5 | VSSQ_7 | G1 |

| B8 | DQU5 | VSSQ_7 |

G9 | A3 | DQU6 | VSSQ_8 | G9 |

| A3 | DQU6 | VSSQ_8 |

|

| DQU7 | VSSQ_9 |

|

|

| DQU7 | VSSQ_9 |

|

|

|

|

|

|

|

|

|

M8 | N3 |

| P7 |

| P3 |

H1 | N2 |

| P8 |

| P2 |

L8 | R8 |

| R2 |

| T8 |

B2 | R3 |

D9 | L7 |

G7 | R7 |

K2 | N7 |

K8 | T3 |

N1 |

|

N9 | M7 |

R1 |

|

R9 | M2 |

| N8 |

| M3 |

A1 |

|

A8 | J 7 |

C1 | K7 |

C9 | K9 |

D2 |

|

E9 | L2 |

F1 | K1 |

H2 | J 3 |

H9 | K3 |

| L3 |

J 1 |

|

J 9 | T2 |

L1 |

|

L9 |

|

T7 | F3 |

| G3 |

A9 | C7 |

B3 | B7 |

E1 |

|

G8 | E7 |

J 2 | D3 |

J 8 |

|

M1 | E3 |

M9 | F7 |

P1 | F2 |

P9 | F8 |

T1 | H3 |

T9 | H8 |

| G2 |

| H7 |

B1 |

|

B9 | D7 |

D1 | C3 |

D8 | C8 |

E2 | C2 |

E8 | A7 |

F9 | A2 |

G1 | B8 |

G9 | A3 |

|

|

A0 | VREFCA | M8 |

| N3 | A0 | VREFCA | ||

|

| P7 | ||||||

A1 |

|

|

| P3 | A1 |

| ||

A2 | VREFDQ | H1 |

| N2 | A2 | VREFDQ | ||

A3 |

|

| P8 | A3 | ||||

A4 |

|

|

| P2 | A4 |

| ||

A5 | ZQ | L8 |

| R8 | A5 | ZQ | ||

A6 |

|

| R2 | A6 | ||||

A7 |

|

|

| T8 | A7 |

| ||

A8 | VDD_1 | B2 |

| R3 | A8 | VDD_1 | ||

A9 | D9 |

| L7 | A9 | ||||

A10/AP | VDD_2 | G7 |

| R7 | A10/AP | VDD_2 | ||

A11 | VDD_3 | K2 |

| N7 | A11 | VDD_3 | ||

A12/BC | VDD_4 | K8 |

| T3 | A12/BC | VDD_4 | ||

A13 | VDD_5 | N1 |

|

| A13 | VDD_5 | ||

|

| VDD_6 | N9 |

| M7 |

|

| VDD_6 |

NC_5 | VDD_7 | R1 |

|

| NC_5 | VDD_7 | ||

|

| VDD_8 | R9 |

| M2 |

|

| VDD_8 |

BA0 | VDD_9 |

|

| N8 | BA0 | VDD_9 | ||

BA1 |

|

|

| M3 | BA1 |

| ||

BA2 | VDDQ_1 | A1 |

| J 7 | BA2 | VDDQ_1 | ||

|

| A8 |

|

|

| |||

CK | VDDQ_2 | C1 |

| K7 | CK | VDDQ_2 | ||

CK | VDDQ_3 | C9 |

| K9 | CK | VDDQ_3 | ||

CKE | VDDQ_4 | D2 |

|

| CKE | VDDQ_4 | ||

|

| VDDQ_5 | E9 |

| L2 |

|

| VDDQ_5 |

CS | VDDQ_6 | F1 |

| K1 | CS | VDDQ_6 | ||

ODT | VDDQ_7 | H2 |

| J 3 | ODT | VDDQ_7 | ||

RAS |

| VDDQ_8 | H9 |

| K3 | RAS |

| VDDQ_8 |

CAS |

| VDDQ_9 |

|

| L3 | CAS |

| VDDQ_9 |

WE | NC_1 | J 1 |

|

| WE | NC_1 | ||

|

| J 9 |

| T2 |

|

| ||

RESET |

| NC_2 | L1 |

|

| RESET |

| NC_2 |

|

| NC_3 | L9 |

|

|

|

| NC_3 |

|

| NC_4 | T7 |

| F3 |

|

| NC_4 |

DQSL |

| NC_6 |

|

| G3 | DQSL |

| NC_6 |

DQSL |

|

|

|

|

| DQSL |

|

|

DQSU | VSS_1 | A9 |

| C7 | DQSU | VSS_1 | ||

B3 |

| B7 | ||||||

DQSU |

| VSS_2 | E1 |

|

| DQSU |

| VSS_2 |

|

| VSS_3 | G8 |

| E7 |

|

| VSS_3 |

DML | VSS_4 | J 2 |

| D3 | DML | VSS_4 | ||

DMU | VSS_5 | J 8 |

|

| DMU | VSS_5 | ||

|

| VSS_6 | M1 |

| E3 |

|

| VSS_6 |

DQL0 | VSS_7 | M9 |

| F7 | DQL0 | VSS_7 | ||

DQL1 | VSS_8 | P1 |

| F2 | DQL1 | VSS_8 | ||

DQL2 | VSS_9 | P9 |

| F8 | DQL2 | VSS_9 | ||

DQL3 | VSS_10 | T1 |

| H3 | DQL3 | VSS_10 | ||

DQL4 | VSS_11 | T9 |

| H8 | DQL4 | VSS_11 | ||

DQL5 | VSS_12 |

|

| G2 | DQL5 | VSS_12 | ||

DQL6 |

|

|

| H7 | DQL6 |

| ||

DQL7 | VSSQ_1 | B1 |

| D7 | DQL7 | VSSQ_1 | ||

|

| B9 |

|

|

| |||

DQU0 | VSSQ_2 | D1 |

| C3 | DQU0 | VSSQ_2 | ||

DQU1 | VSSQ_3 | D8 |

| C8 | DQU1 | VSSQ_3 | ||

DQU2 | VSSQ_4 | E2 |

| C2 | DQU2 | VSSQ_4 | ||

DQU3 | VSSQ_5 | E8 |

| A7 | DQU3 | VSSQ_5 | ||

DQU4 | VSSQ_6 | F9 |

| A2 | DQU4 | VSSQ_6 | ||

DQU5 | VSSQ_7 | G1 |

| B8 | DQU5 | VSSQ_7 | ||

DQU6 | VSSQ_8 | G9 |

| A3 | DQU6 | VSSQ_8 | ||

DQU7 | VSSQ_9 |

|

|

| DQU7 | VSSQ_9 | ||

|

|

|

|

|

|

|

|

|

M8

H1

L8

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

J 1 J 9 L1 L9 T7

A9

B3

E1

G8 J 2 J 8 M1 M9 P1 P9 T1 T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

THE ![]() SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM

SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM

EMEA INTERACTIVE

|

|

|

|

|

|

| GP4_MSTAR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2011 . 08 . 21 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

| DDR |

|

|

|

|

|

|

|

|

|

|

| 1 2 | 2 0 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

Copyright © 2012 LG Electronics. Inc. All rights reserved. | LGE Internal Use Only |

Only for training and service purposes |

|