PM8385

QuadPHY RT

Released

GENERAL

•Supports four physical interfaces for Gigabit Ethernet at 1.25 Gbit/s per IEEE 802.3z or Fibre Channel physical interfaces at 1.0625 or 2.125 Gbit/s per Fibre Channel Physical Interface (FC- PI) for repeating or retiming applications.

•Backplane repeating/retiming signal integrity features enable standards compliance, link extension and robust

•Provides direct connection to high- speed serial backplanes, coax stacking cables, or optical / copper Small Form Factor Pluggable (SFP) modules.

•Provides

•Fast

•Rate

•Extensive per port backplane monitoring for loss of signal, error rates, and link level violations.

•Supports

HIGH-SPEED INTERFACE

•

•Programmable receive input equalization provides robust data recovery of highly degraded input signals.

•Minimal board footprint and exceptional signal integrity achieved:

•No external components are required to interface the

•Programmable receive input termination of 100 ohm or 150 ohm differential.

•Programmable output impedance of 100 ohm or 150 ohm differential.

TEST AND CONTROL

•Digital loss of link (DLOL) detect pin provides status output for monitoring individual or multiple links.

•DLOL and optional interrupt pin can be programmed to indicate:

•Analog loss of signal.

•Excessive 8B/10B code and disparity violations.

•Fibre Channel comma density.

•Loss of synchronization to detect Gigabit Ethernet or Fibre Channel framing errors.

•Internal packet generator and comparator features simplify backplane and jitter testing via:

•Programmable pattern (can be used with GE high, low and mixed frequency tests).

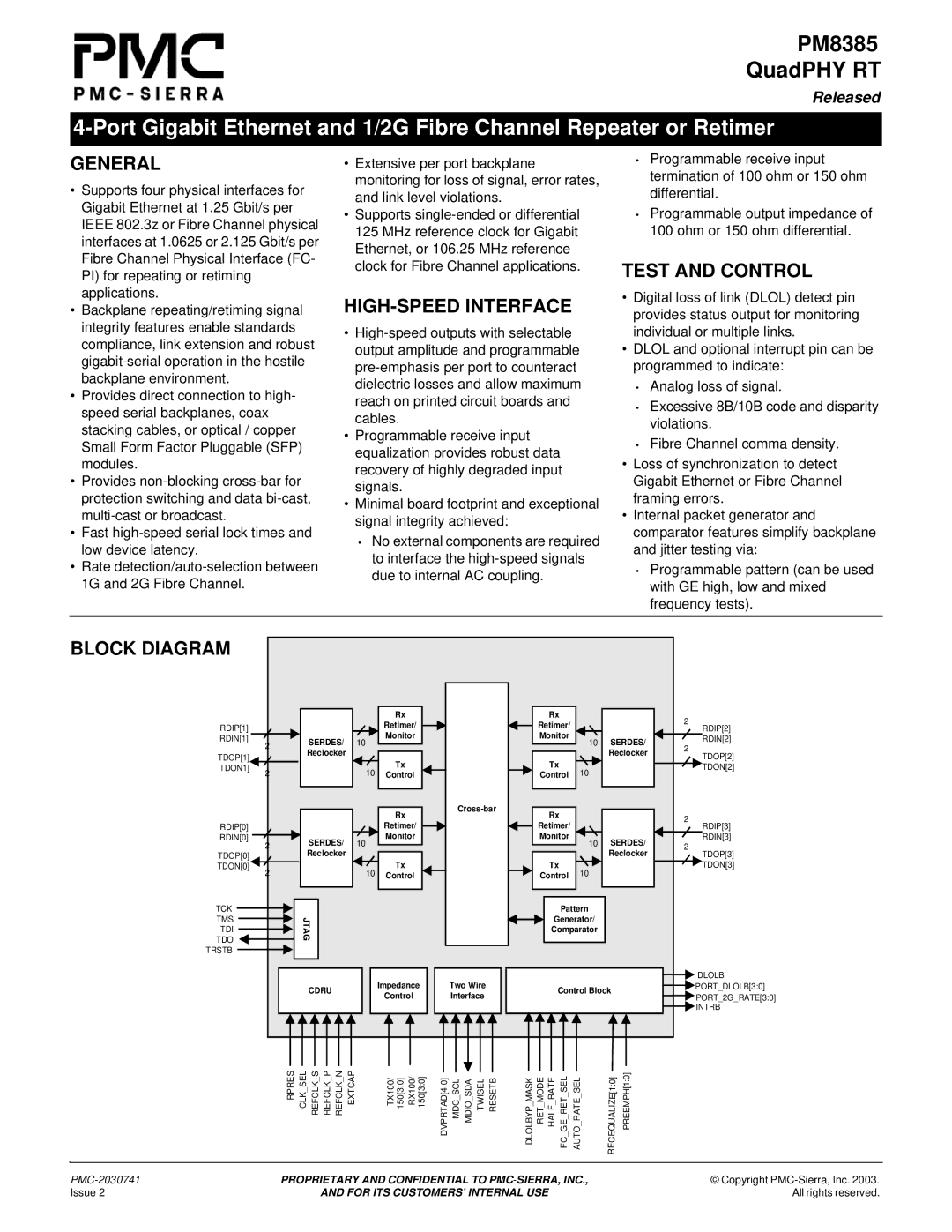

BLOCK DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Rx |

|

|

|

|

| Rx |

|

|

| 2 |

RDIP[1] |

|

|

|

|

| Retimer/ |

|

|

|

|

| Retimer/ |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| RDIP[2] | |||

|

|

|

|

| Monitor |

|

|

|

|

| Monitor |

|

|

| ||

RDIN[1] |

|

| SERDES/ |

| 10 |

|

|

|

|

| 10 | SERDES/ | RDIN[2] | |||

2 |

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

| 2 | ||||||

|

| Reclocker |

|

|

|

|

|

|

|

|

|

| Reclocker | |||

TDOP[1] |

|

|

|

|

|

|

|

|

|

|

|

| TDOP[2] | |||

|

|

|

|

| Tx |

|

|

|

|

| Tx |

|

|

| ||

TDON1] | 2 |

|

|

| 10 |

|

|

|

|

| 10 |

|

| TDON[2] | ||

|

|

| Control |

|

|

|

|

| Control |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| Rx |

|

|

| Rx |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 | ||

|

|

|

|

|

| Retimer/ |

|

|

|

|

| Retimer/ |

|

|

| |

RDIP[0] |

|

|

|

|

|

|

|

|

|

|

|

|

| RDIP[3] | ||

RDIN[0] | 2 |

| SERDES/ |

| 10 | Monitor |

|

|

|

|

| Monitor | 10 | SERDES/ | RDIN[3] | |

|

|

|

|

|

|

|

|

|

| 2 | ||||||

TDOP[0] |

|

| Reclocker |

|

|

|

|

|

|

|

|

|

| Reclocker | TDOP[3] | |

TDON[0] | 2 |

|

|

| 10 | Tx |

|

|

|

|

| Tx | 10 |

|

| TDON[3] |

|

|

|

| Control |

|

|

|

|

| Control |

|

|

| |||

TCK |

|

|

|

|

|

|

|

|

|

|

| Pattern |

|

|

| |

TMS |

| JTAG |

|

|

|

|

|

|

|

| Generator/ |

|

|

| ||

TDI |

|

|

|

|

|

|

|

|

| Comparator |

|

|

| |||

TDO |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

TRSTB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Impedance |

| Two Wire |

|

|

|

|

|

| DLOLB | |

|

|

| CDRU |

|

|

|

|

| Control Block |

| PORT_DLOLB[3:0] | |||||

|

|

|

|

| Control |

|

| Interface |

|

|

| PORT_2G_RATE[3:0] | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| INTRB |

| RPRES | CLK SEL | REFCLK S REFCLK P REFCLK N | EXTCAP |

| TX100/ 150[3:0] RX100/ | 150[3:0] | DVPRTAD[4:0] | MDC SCL MDIO SDA TWISEL | RESETB | DLOLBYP MASK | RET MODE HALF RATE FC GE RET SEL | AUTO RATE SEL | E[1:0] | PREEMPH[1:0] |

|

|

| RECEQUALIZ |

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

PROPRIETARY AND CONFIDENTIAL TO | © Copyright | |

Issue 2 | AND FOR ITS CUSTOMERS’ INTERNAL USE | All rights reserved. |