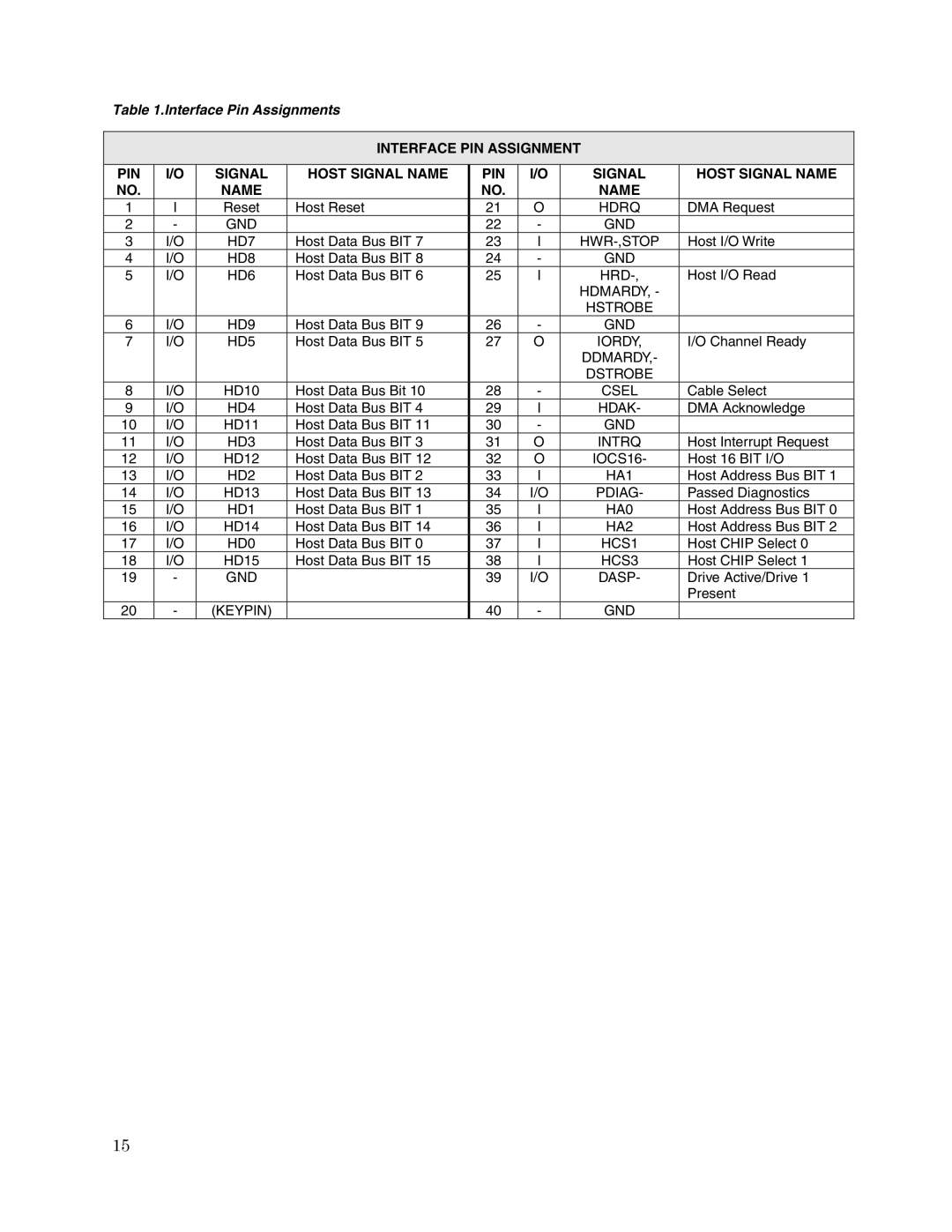

Table 1.Interface Pin Assignments

INTERFACE PIN ASSIGNMENT

PIN | I/O | SIGNAL | HOST SIGNAL NAME | PIN | I/O |

NO. |

| NAME |

| NO. |

|

1 | I | Reset | Host Reset | 21 | O |

2 | - | GND |

| 22 | - |

3 | I/O | HD7 | Host Data Bus BIT 7 | 23 | I |

4 | I/O | HD8 | Host Data Bus BIT 8 | 24 | - |

5 | I/O | HD6 | Host Data Bus BIT 6 | 25 | I |

|

|

|

|

|

|

6 | I/O | HD9 | Host Data Bus BIT 9 | 26 | - |

7 | I/O | HD5 | Host Data Bus BIT 5 | 27 | O |

|

|

|

|

|

|

8 | I/O | HD10 | Host Data Bus Bit 10 | 28 | - |

9 | I/O | HD4 | Host Data Bus BIT 4 | 29 | I |

10 | I/O | HD11 | Host Data Bus BIT 11 | 30 | - |

11 | I/O | HD3 | Host Data Bus BIT 3 | 31 | O |

12 | I/O | HD12 | Host Data Bus BIT 12 | 32 | O |

13 | I/O | HD2 | Host Data Bus BIT 2 | 33 | I |

14 | I/O | HD13 | Host Data Bus BIT 13 | 34 | I/O |

15 | I/O | HD1 | Host Data Bus BIT 1 | 35 | I |

16 | I/O | HD14 | Host Data Bus BIT 14 | 36 | I |

17 | I/O | HD0 | Host Data Bus BIT 0 | 37 | I |

18 | I/O | HD15 | Host Data Bus BIT 15 | 38 | I |

19 | - | GND |

| 39 | I/O |

|

|

|

|

|

|

20 | - | (KEYPIN) |

| 40 | - |

SIGNAL

NAME

HDRQ

GND

GND

HDMARDY, -

HSTROBE

GND

IORDY,

DDMARDY,-

DSTROBE

CSEL

HDAK-

GND

INTRQ

IOCS16-

HA1

PDIAG-

HA0

HA2

HCS1

HCS3

DASP-

GND

HOST SIGNAL NAME

DMA Request

Host I/O Write

Host I/O Read

I/O Channel Ready

Cable Select

DMA Acknowledge

Host Interrupt Request

Host 16 BIT I/O

Host Address Bus BIT 1

Passed Diagnostics

Host Address Bus BIT 0

Host Address Bus BIT 2

Host CHIP Select 0

Host CHIP Select 1

Drive Active/Drive 1 Present

15