INSTRUCTION SET

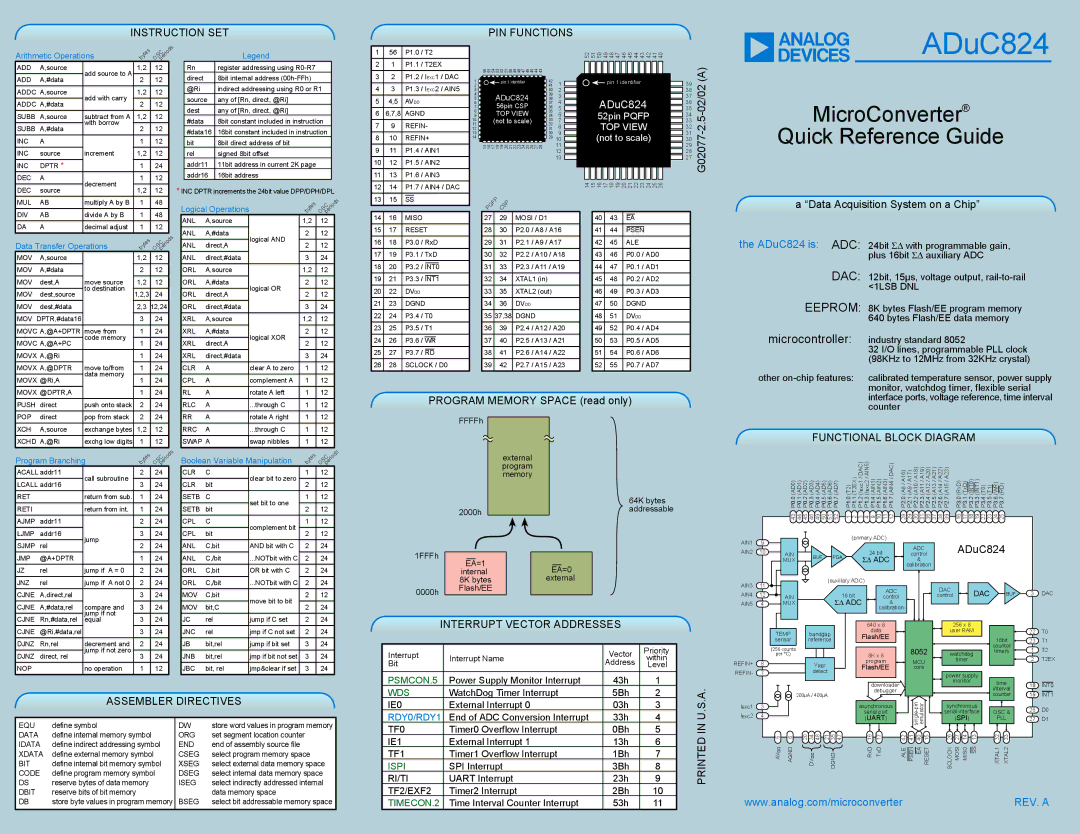

PIN FUNCTIONS

ADuC824 |

Arithmetic Operations | bytes | OSCperiods | |||

ADD | A,source | add source to A | 1,2 | 12 | |

ADD | A,#data | 2 | 12 | ||

| |||||

ADDC | A,source | add with carry | 1,2 | 12 | |

ADDC A,#data | 2 | 12 | |||

| |||||

SUBB | A,source | subtract from A | 1,2 | 12 | |

SUBB | A,#data | with borrow | 2 | 12 | |

| |||||

INC | A |

| 1 | 12 | |

INC | source | increment | 1,2 | 12 | |

INC | DPTR * |

| 1 | 24 | |

DEC | A |

| 1 | 12 | |

|

| Legend | ||||

| Rn | register addressing using |

| |||

| direct | 8bit internal address |

| |||

| @Ri | indirect addressing using R0 or R1 |

| |||

| source | any of [Rn, direct, @Ri] |

| |||

| dest | any of [Rn, direct, @Ri] |

| |||

| #data | 8bit constant included in instruction |

| |||

| #data16 | 16bit constant included in instruction |

| |||

| bit | 8bit direct address of bit |

| |||

| rel | signed 8bit offset |

| |||

| addr11 | 11bit address in current 2K page |

| |||

| addr16 | 16bit address |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

156 P1.0 / T2

21 P1.1 / T2EX

32 P1.2 / IEXC1 / DAC

43 P1.3 / IEXC2 / AIN5

54,5 AVDD

66,7,8 AGND

79 REFIN-

810 REFIN+

911 P1.4 / AIN1

10 | 12 | P1.5 / AIN2 | ||||||

11 | 13 | P1.6 / AIN3 | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 52 51 50 49 48 47 46 45 44 43 42 41 40 |

|

|

| |||||||||||||

| 56 55 54 53 52 51 50 49 48 47 46 45 44 43 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

1 |

|

| pin 1 identifier | 42 | 1 |

|

|

|

|

|

|

| pin 1 identifier |

| 39 | |||||||||||||

2 |

|

|

|

|

| 41 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

3 |

|

|

|

|

| 40 | 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 38 | |

4 |

|

| ADuC824 | 39 | 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 37 | |||

5 |

|

| 38 |

|

|

|

|

|

| ADuC824 |

| |||||||||||||||||

7 |

|

| 56pin CSP | 36 | 5 |

|

|

|

|

|

|

| 35 | |||||||||||||||

6 |

|

|

|

|

| 37 | 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 36 | |

8 |

|

| TOP VIEW | 35 | 6 |

|

|

|

|

|

| 52pin PQFP |

| 34 | ||||||||||||||

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

9 |

|

| 34 |

|

|

|

|

|

|

| ||||||||||||||||||

10 |

| (not to scale) | 33 | 7 |

|

|

|

|

|

|

| 33 | ||||||||||||||||

11 |

| 32 |

|

|

|

|

|

| TOP VIEW |

| ||||||||||||||||||

12 |

|

|

|

|

| 31 | 8 |

|

|

|

|

|

|

| 32 | |||||||||||||

13 |

|

|

|

|

| 30 | 9 |

|

|

|

|

|

| (not to scale) |

| 31 | ||||||||||||

14 |

|

|

|

|

| 29 | 10 |

|

|

|

|

|

|

| 30 | |||||||||||||

| 15 16 17 18 19 20 21 22 23 24 25 26 27 28 |

|

| 11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 29 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

| 12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 28 |

|

|

|

|

|

|

|

| 13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MicroConverter® | ||

2.5- | Quick Reference Guide | |

G02077 | ||

|

DEC | source | decrement | 1,2 | 12 |

| ||||

MUL | AB | multiply A by B | 1 | 48 |

DIV | AB | divide A by B | 1 | 48 |

DA | A | decimal adjust | 1 | 12 |

Data Transfer Operations | bytes | OSCperiods | ||

MOV | A,source |

| 1,2 | 12 |

MOV | A,#data |

| 2 | 12 |

MOV | dest,A | move source | 1,2 | 12 |

MOV | dest,source | to destination | 1,2,3 | 24 |

| ||||

MOV | dest,#data |

| 2,3 12,24 | |

MOV DPTR,#data16 |

| 3 | 24 | |

MOVC A,@A+DPTR move from | 1 | 24 | ||

MOVC A,@A+PC | code memory | 1 | 24 | |

| ||||

MOVX A,@Ri |

| 1 | 24 | |

MOVX A,@DPTR | move to/from | 1 | 24 | |

MOVX @Ri,A | data memory | 1 | 24 | |

| ||||

MOVX @DPTR,A |

| 1 | 24 | |

*INC DPTR increments the 24bit value DPP/DPH/DPL

Logical Operations |

| bytes | OSCperiods | ||

ANL | A,source |

| 1,2 | 12 | |

ANL | A,#data | logical AND | 2 | 12 | |

ANL | direct,A | 2 | 12 | ||

| |||||

ANL | direct,#data |

| 3 | 24 | |

ORL | A,source |

| 1,2 | 12 | |

ORL | A,#data | logical OR | 2 | 12 | |

ORL | direct,A | 2 | 12 | ||

| |||||

ORL | direct,#data |

| 3 | 24 | |

XRL | A,source |

| 1,2 | 12 | |

XRL | A,#data | logical XOR | 2 | 12 | |

XRL | direct,A | 2 | 12 | ||

| |||||

XRL | direct,#data |

| 3 | 24 | |

CLR | A | clear A to zero | 1 | 12 | |

CPL | A | complement A | 1 | 12 | |

RL | A | rotate A left | 1 | 12 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 | 14 | P1.7 | / AIN4 / DAC |

| |

|

|

|

|

|

|

13 | 15 | SS |

|

|

|

14 | 16 | MISO |

| ||

15 | 17 | RESET |

| ||

16 | 18 | P3.0 | / RxD |

| |

17 | 19 | P3.1 | / TxD |

| |

18 | 20 | P3.2 | / INT0 |

| |

19 | 21 | P3.3 | / INT1 |

| |

20 | 22 | DVDD |

|

|

|

21 | 23 | DGND |

| ||

22 | 24 | P3.4 | / T0 |

| |

23 | 25 | P3.5 | / T1 |

| |

24 | 26 | P3.6 | / WR |

| |

25 | 27 | P3.7 | / RD |

| |

26 | 28 | SCLOCK / D0 |

| ||

|

|

|

|

|

|

PQFP CSP

2729 MOSI / D1

2830 P2.0 / A8 / A16

2931 P2.1 / A9 / A17

3032 P2.2 / A10 / A18

3133 P2.3 / A11 / A19

3234 XTAL1 (in)

3335 XTAL2 (out)

3436 DVDD

3537,38 DGND

3639 P2.4 / A12 / A20

3740 P2.5 / A13 / A21

3841 P2.6 / A14 / A22

3942 P2.7 / A15 / A23

14 15 16 17 18 19 20 21 22 23 24 25 26

40 | 43 | EA |

41 | 44 | PSEN |

42 | 45 | ALE |

4346 P0.0 / AD0

4447 P0.1 / AD1

4548 P0.2 / AD2

4649 P0.3 / AD3

4750 DGND

4851 DVDD

4952 P0.4 / AD4

5053 P0.5 / AD5

5154 P0.6 / AD6

5255 P0.7 / AD7

a “Data Acquisition System on a Chip” | |

the ADuC824 is: ADC: 24bit ΣΔ with programmable gain, | |

| plus 16bit ΣΔ auxiliary ADC |

DAC: 12bit, 15µs, voltage output, | |

| <1LSB DNL |

EEPROM: | 8K bytes Flash/EE program memory |

| 640 bytes Flash/EE data memory |

microcontroller: | industry standard 8052 |

| 32 I/O lines, programmable PLL clock |

| (98KHz to 12MHz from 32KHz crystal) |

other | calibrated temperature sensor, power supply |

| monitor, watchdog timer, flexible serial |

PUSH | direct | push onto stack | 2 | 24 |

POP | direct | pop from stack | 2 | 24 |

XCH | A,source | exchange bytes | 1,2 | 12 |

XCHD | A,@Ri | exchg low digits | 1 | 12 |

RLC | A | ...through C | 1 | 12 |

RR | A | rotate A right | 1 | 12 |

RRC | A | ...through C | 1 | 12 |

SWAP A | swap nibbles | 1 | 12 | |

PROGRAM MEMORY SPACE (read only)

FFFFh |

interface ports, voltage reference, time interval |

counter |

FUNCTIONAL BLOCK DIAGRAM

Program Branching |

| bytes | OSCperiods | |||

ACALL addr11 | call subroutine | 2 | 24 | |||

LCALL addr16 | 3 | 24 | ||||

|

| |||||

RET |

| return from sub. | 1 | 24 | ||

RETI |

| return from int. | 1 | 24 | ||

AJMP | addr11 |

|

| 2 | 24 | |

LJMP | addr16 | jump |

| 3 | 24 | |

SJMP | rel |

| 2 | 24 | ||

|

| |||||

JMP | @A+DPTR |

|

| 1 | 24 | |

JZ | rel | jump if | A = 0 | 2 | 24 | |

JNZ | rel | jump if | A not 0 | 2 | 24 | |

CJNE | A,direct,rel |

|

| 3 | 24 | |

CJNE | A,#data,rel | compare and | 3 | 24 | ||

CJNE | Rn,#data,rel | jump if not | 3 | 24 | ||

equal |

| |||||

CJNE | @Ri,#data,rel |

|

| 3 | 24 | |

DJNZ | Rn,rel | decrement and | 2 | 24 | ||

DJNZ | direct, rel | jump if not zero | 3 | 24 | ||

|

| |||||

NOP |

| no operation | 1 | 12 | ||

Boolean Variable Manipulation | bytes | OSCperiods | |||

CLR | C | clear bit to zero | 1 | 12 | |

CLR | bit | 2 | 12 | ||

| |||||

SETB | C | set bit to one | 1 | 12 | |

SETB | bit | 2 | 12 | ||

| |||||

CPL | C | complement bit | 1 | 12 | |

CPL | bit | 2 | 12 | ||

| |||||

ANL | C,bit | AND bit with C | 2 | 24 | |

ANL | C,/bit | ...NOTbit with C | 2 | 24 | |

ORL | C,bit | OR bit with C | 2 | 24 | |

ORL | C,/bit | ...NOTbit with C | 2 | 24 | |

MOV | C,bit | move bit to bit | 2 | 12 | |

MOV | bit,C | 2 | 24 | ||

| |||||

JC | rel | jump if C set | 2 | 24 | |

JNC | rel | jmp if C not set | 2 | 24 | |

JB | bit,rel | jump if bit set | 3 | 24 | |

JNB | bit,rel | jmp if bit not set | 3 | 24 | |

JBC | bit, rel | jmp&clear if set | 3 | 24 | |

|

| external |

|

|

| |

|

| program |

|

|

| |

|

| memory |

|

|

| |

|

|

|

|

| 64K bytes | |

|

| 2000h |

| addressable | ||

|

|

|

|

| ||

1FFFh |

|

|

|

|

|

|

| EA=1 |

| EA=0 |

|

| |

|

|

|

|

| ||

|

| internal |

|

|

| |

|

| 8K bytes |

| external |

|

|

0000h |

| Flash/EE |

|

|

|

|

| INTERRUPT VECTOR ADDRESSES |

| ||||

|

|

|

|

|

|

|

Interrupt |

| Interrupt Name |

| Vector | Priority | |

|

| within | ||||

Bit |

|

|

|

| Address | Level |

|

|

|

|

| ||

PSMCON.5 |

| Power Supply Monitor Interrupt | 43h | 1 | ||

WDS |

| WatchDog Timer Interrupt | 5Bh | 2 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (AD0) | (AD1) (AD2) (AD3) (AD4) (AD5) (AD6) | (AD7) |

| (T2EX) | 1 / DAC) | 2 / AIN5) | (AIN1) (AIN2) (AIN3) (AIN4 / DAC) | (A8 / A16) | (A9 / A17) | (A10 / A18) | (A11 / A19) | (A12 / A20) | (A13 / A21) | (A14 / A22) | (A15 / A23) | (RxD) (TxD) (INT0) (INT1) (T0) (T1) | (WR) | (RD) |

|

| |||||||||||||

|

| (T2) | EXC | EXC |

|

| |||||||||||||||||||||||||||||

|

| (I | (I |

|

| ||||||||||||||||||||||||||||||

|

| P0.0 | P0.1 | P0.2 | P0.3 | P0.4 | P0.5 | P0.6 | P0.7 | P1.0 | P1.1 | P1.2 | P1.3 | P1.4 | P1.5 | P1.6 | P1.7 | P2.0 | P2.1 | P2.2 | P2.3 | P2.4 | P2.5 | P2.6 | P2.7 | P3.0 | P3.1 | P3.2 | P3.3 | P3.4 | P3.5 | P3.6 | P3.7 |

|

|

|

| 43 44 45 46 49 50 51 52 | 1 2 3 4 9 | 10 11 12 | 28 29 30 31 36 37 38 39 | 16 17 18 19 22 23 24 25 |

|

| |||||||||||||||||||||||||||

AIN1 | 9 |

|

|

|

|

|

|

|

|

| (primary ADC) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ADC |

|

|

|

| ADuC824 |

|

| ||||||||||

AIN2 | 10 |

|

|

|

|

|

|

|

|

|

|

|

| 24 bit |

|

|

|

|

|

|

|

|

|

| |||||||||||

AIN |

|

| BUF |

| PGA |

|

|

|

|

|

| control |

|

|

|

|

| ||||||||||||||||||

|

| MUX |

|

|

|

| ΣΔ ADC |

|

| & |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| calibration |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

AIN3 | 11 |

|

|

|

|

|

| (auxillary ADC) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ADC |

|

|

|

|

|

| DAC |

|

|

|

|

|

|

|

|

| |||||

AIN4 | 12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DAC |

| BUF | 3 | DAC | |||||||

AIN |

|

|

|

|

|

|

| 16 bit |

|

|

|

| control |

|

|

|

|

|

| control |

|

|

| ||||||||||||

AIN5 | 4 | MUX |

|

|

|

|

|

| ΣΔ ADC |

|

|

|

| & |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| calibration |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| 640 x 8 |

|

|

|

|

|

|

|

|

| 256 x 8 |

|

|

|

|

|

|

| |||||

|

| TEMP |

|

| bandgap |

|

|

|

|

| data |

|

|

|

|

|

|

|

|

|

| user RAM |

|

|

|

| 22 | T0 | |||||||

|

|

|

|

|

|

| Flash/EE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

| sensor |

|

| reference |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16bit | 23 | T1 | ||||||||||

|

| (256 counts |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8052 |

|

|

|

|

|

|

|

|

| counter | 1 | T2 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| watchdog |

|

|

| timers | ||||||||||

|

| per oC) |

|

|

|

|

|

|

|

|

|

| 8K x 8 |

|

|

|

|

|

|

|

|

|

| ||||||||||||

REFIN+ | 8 |

|

|

|

| VREF |

|

|

|

|

| program |

|

|

| MCU |

|

|

|

| timer |

|

|

|

|

|

| 2 | T2EX | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

REFIN- | 7 |

|

|

|

|

|

|

|

| Flash/EE |

|

| core |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

| detect |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| power supply |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| downloader |

|

|

|

|

|

|

|

| monitor |

|

|

| time | 18 | INT0 | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

| 200µA / 400µA |

|

|

|

|

| debugger |

|

|

|

|

|

|

|

|

|

|

|

|

|

| interval | 19 | INT1 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| counter | |||||||||

ASSEMBLER DIRECTIVES

EQU | define symbol | DW | store word values in program memory |

DATA | define internal memory symbol | ORG | set segment location counter |

IDATA | define indirect addressing symbol | END | end of assembly source file |

XDATA | define external memory symbol | CSEG | select program memory space |

BIT | define internal bit memory symbol | XSEG | select external data memory space |

CODE | define program memory symbol | DSEG | select internal data memory space |

DS | reserve bytes of data memory | ISEG | select indirectly addressed internal |

DBIT | reserve bits of bit memory |

| data memory space |

DB | store byte values in program memory | BSEG | select bit addressable memory space |

IE0 | External Interrupt 0 | 03h | 3 |

RDY0/RDY1 | End of ADC Conversion Interrupt | 33h | 4 |

TF0 | Timer0 Overflow Interrupt | 0Bh | 5 |

IE1 | External Interrupt 1 | 13h | 6 |

TF1 | Timer1 Overflow Interrupt | 1Bh | 7 |

ISPI | SPI Interrupt | 3Bh | 8 |

RI/TI | UART Interrupt | 23h | 9 |

TF2/EXF2 | Timer2 Interrupt | 2Bh | 10 |

TIMECON.2 | Time Interval Counter Interrupt | 53h | 11 |

U.S.A.IN | IEXC1 | 3 |

|

|

|

|

| asynchronous |

| synchronous |

| 26 | D0 | |

IEXC2 | 4 |

|

|

|

|

| serial port |

| serial interface | OSC & | ||||

|

|

|

|

| (UART) |

| (SPI) | PLL | 27 | D1 | ||||

|

|

|

|

|

|

|

| |||||||

|

|

| 20 | 34 | 48 | 21 DGND 35 47 | RxD 16 TxD 17 |

| SCLOCK 26 MOSI 27 MISO 14 SS 13 | XTAL1 32 XTAL2 33 |

|

| ||

PRINTED |

| 5 | AGND 6 | ALE 42 | PSEN 41 EA 40 RESET 15 |

|

| |||||||

| DD | DD |

|

| ||||||||||

| AV | DV |

|

| ||||||||||

| www.analog.com/microconverter |

|

|

| REV. A | |||||||||