Q87M vPro

DRAM Timing Configuration

DRAM Frequency

If [Auto] is selected, the motherboard will detect the memory module(s) inserted and assign the appropriate frequency automatically.

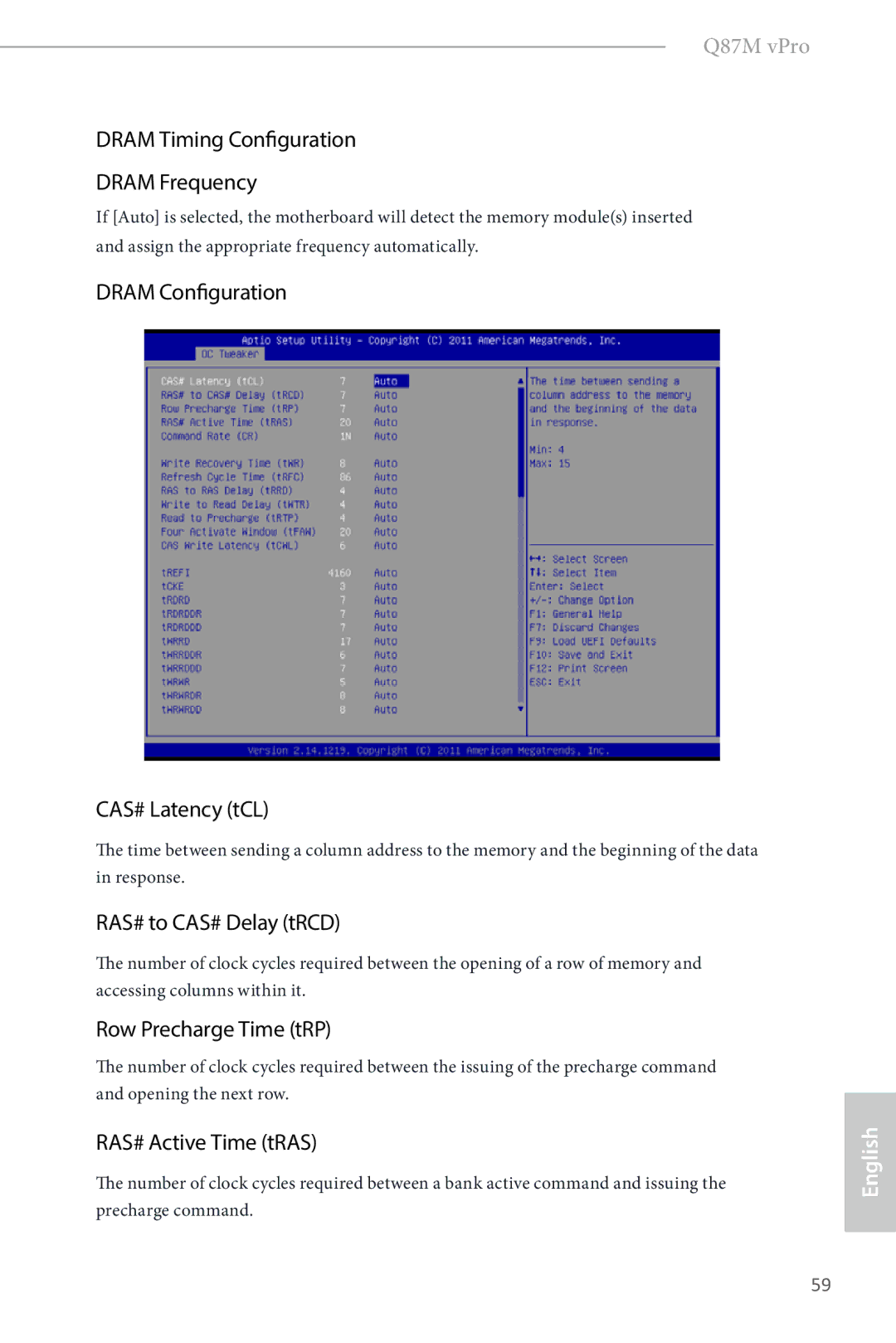

DRAM Configuration

CAS# Latency (tCL)

The time between sending a column address to the memory and the beginning of the data in response.

RAS# to CAS# Delay (tRCD)

The number of clock cycles required between the opening of a row of memory and accessing columns within it.

Row Precharge Time (tRP)

The number of clock cycles required between the issuing of the precharge command and opening the next row.

RAS# Active Time (tRAS)

The number of clock cycles required between a bank active command and issuing the precharge command.

English

59