Implementing MLC NAND Flash for

MultiBurst

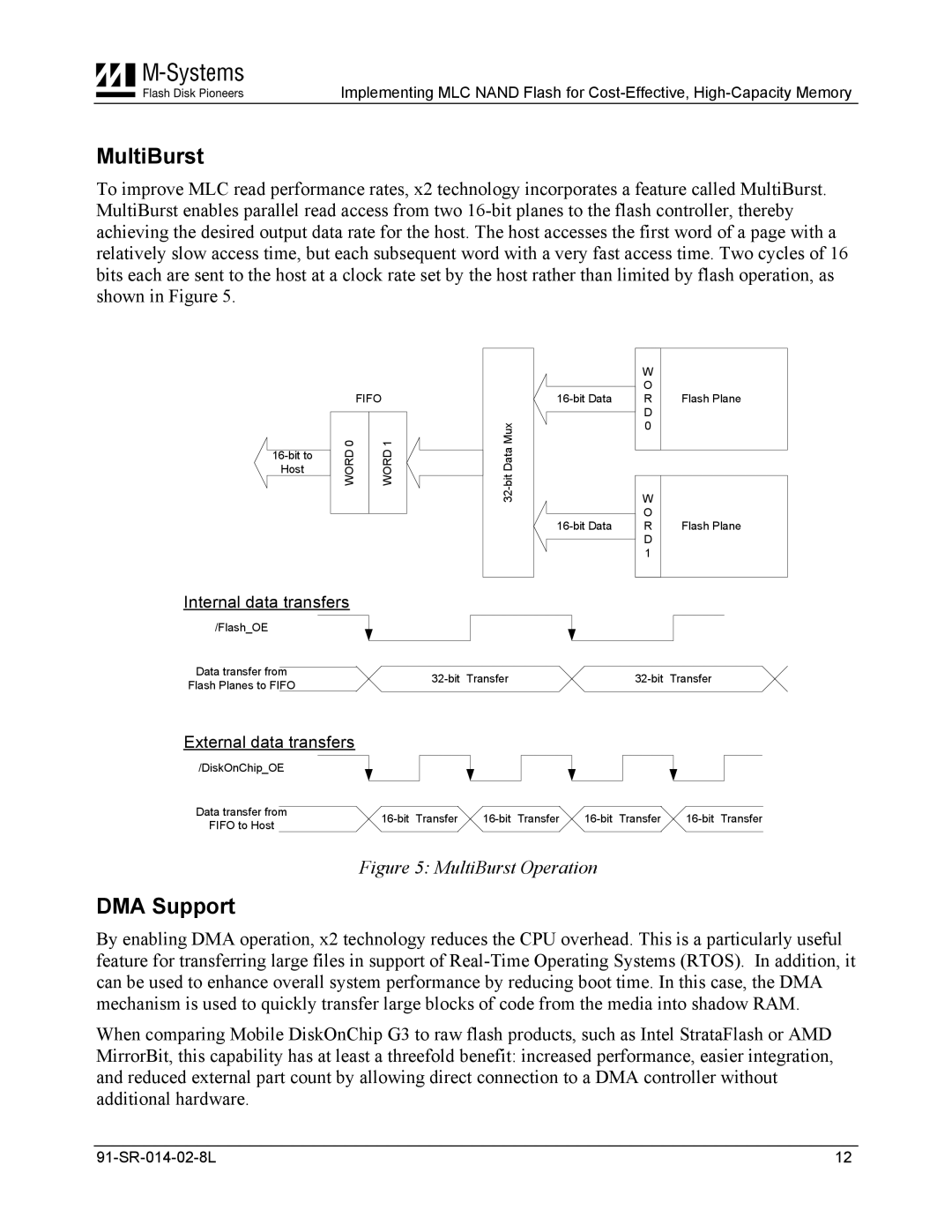

To improve MLC read performance rates, x2 technology incorporates a feature called MultiBurst. MultiBurst enables parallel read access from two

|

| FIFO |

| ||

|

|

|

|

| Mux |

| 0 |

| 1 |

| |

WORD |

| WORD |

| ||

Host |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Internal data transfers

/Flash_OE |

|

|

| |

|

| |||

Data transfer from |

|

| ||

Flash Planes to FIFO | ||||

|

| |||

External data transfers

| W |

|

O | Flash Plane | |

R | ||

| D |

|

| 0 |

|

|

|

|

| W |

|

O | Flash Plane | |

R | ||

| D |

|

| 1 |

|

|

|

|

/DiskOnChip_OE |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |||

Data transfer from |

|

|

|

|

|

|

|

| ||

FIFO to Host | ||||||||||

|

|

|

|

|

|

|

| |||

Figure 5: MultiBurst Operation

DMA Support

By enabling DMA operation, x2 technology reduces the CPU overhead. This is a particularly useful feature for transferring large files in support of

When comparing Mobile DiskOnChip G3 to raw flash products, such as Intel StrataFlash or AMD MirrorBit, this capability has at least a threefold benefit: increased performance, easier integration, and reduced external part count by allowing direct connection to a DMA controller without additional hardware.

12 |