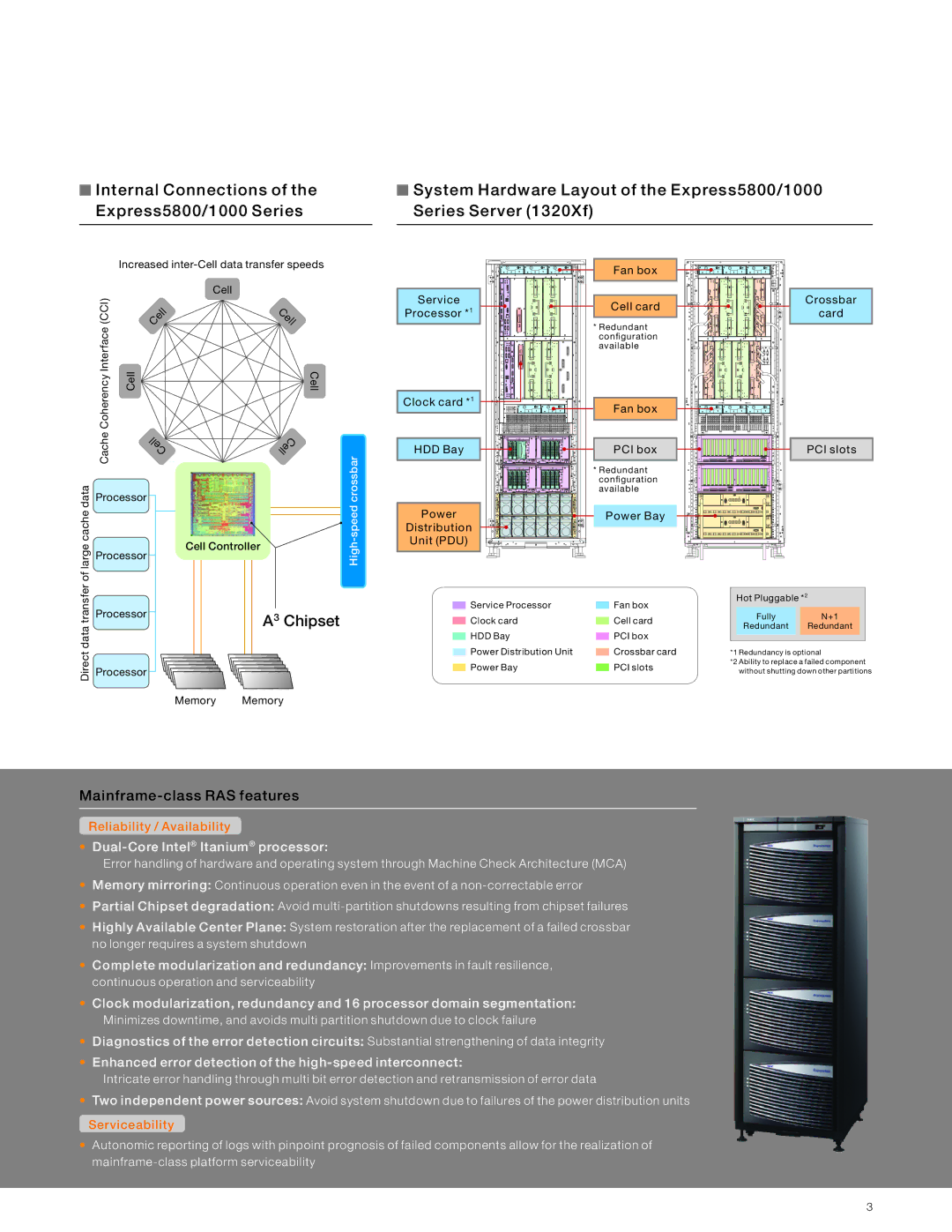

n Internal Connections of the | n System Hardware Layout of the Express5800/1000 | |

Express5800/1000 Series | Series Server (1320Xf) | |

|

|

|

Direct data transfer of large cache data

Increased

Cell

(CCI) |

| Cell | Cell |

Coherency Interface | Cell |

| Cell |

Cache |

| Cell | Cell |

Processor |

|

| |

Processor | Cell Controller | ||

|

| ||

Processor |

| A3 Chipset | |

|

|

| |

Processor |

|

| |

|

| Memory | Memory |

Service

Processor *1

Clock card *1 |

HDD Bay

Power

Distribution

Unit (PDU)

![]() Service Processor

Service Processor

![]() Clock card

Clock card

![]() HDD Bay

HDD Bay

![]() Power Distribution Unit

Power Distribution Unit

![]() Power Bay

Power Bay

Fan box

Cell card

* Redundant configuration available

Fan box

PCI box

*Redundant configuration available

Power Bay

![]() Fan box

Fan box

![]() Cell card

Cell card

![]() PCI box

PCI box

![]() Crossbar card

Crossbar card

![]() PCI slots

PCI slots

Crossbar

card

PCI slots

Hot Pluggable *2

FullyN+1

Redundant Redundant

*1 Redundancy is optional

*2 Ability to replace a failed component without shutting down other partitions

Mainframe-class RAS features

Reliability / Availability

•Dual-Core Intel® Itanium® processor:

Error handling of hardware and operating system through Machine Check Architecture (MCA)

•Memory mirroring: Continuous operation even in the event of a

•Partial Chipset degradation: Avoid

•Highly Available Center Plane: System restoration after the replacement of a failed crossbar no longer requires a system shutdown

•Complete modularization and redundancy: Improvements in fault resilience, continuous operation and serviceability

•Clock modularization, redundancy and 16 processor domain segmentation: Minimizes downtime, and avoids multi partition shutdown due to clock failure

•Diagnostics of the error detection circuits: Substantial strengthening of data integrity

•Enhanced error detection of the

Intricate error handling through multi bit error detection and retransmission of error data

•Two independent power sources: Avoid system shutdown due to failures of the power distribution units

Serviceability

•Autonomic reporting of logs with pinpoint prognosis of failed components allow for the realization of

3