![]()

Features for performance improvement

At the heart of the Express5800/1000 series server is the

The system has been equipped with the NEC designed chipset, “A3 ”, in order to improve performance by utilizing, to its full extent, the massive 24MB of cache memory that has been built into the

Technologies to increase

to maximize the performance for enterprise mission critical[1080Rf] computing.

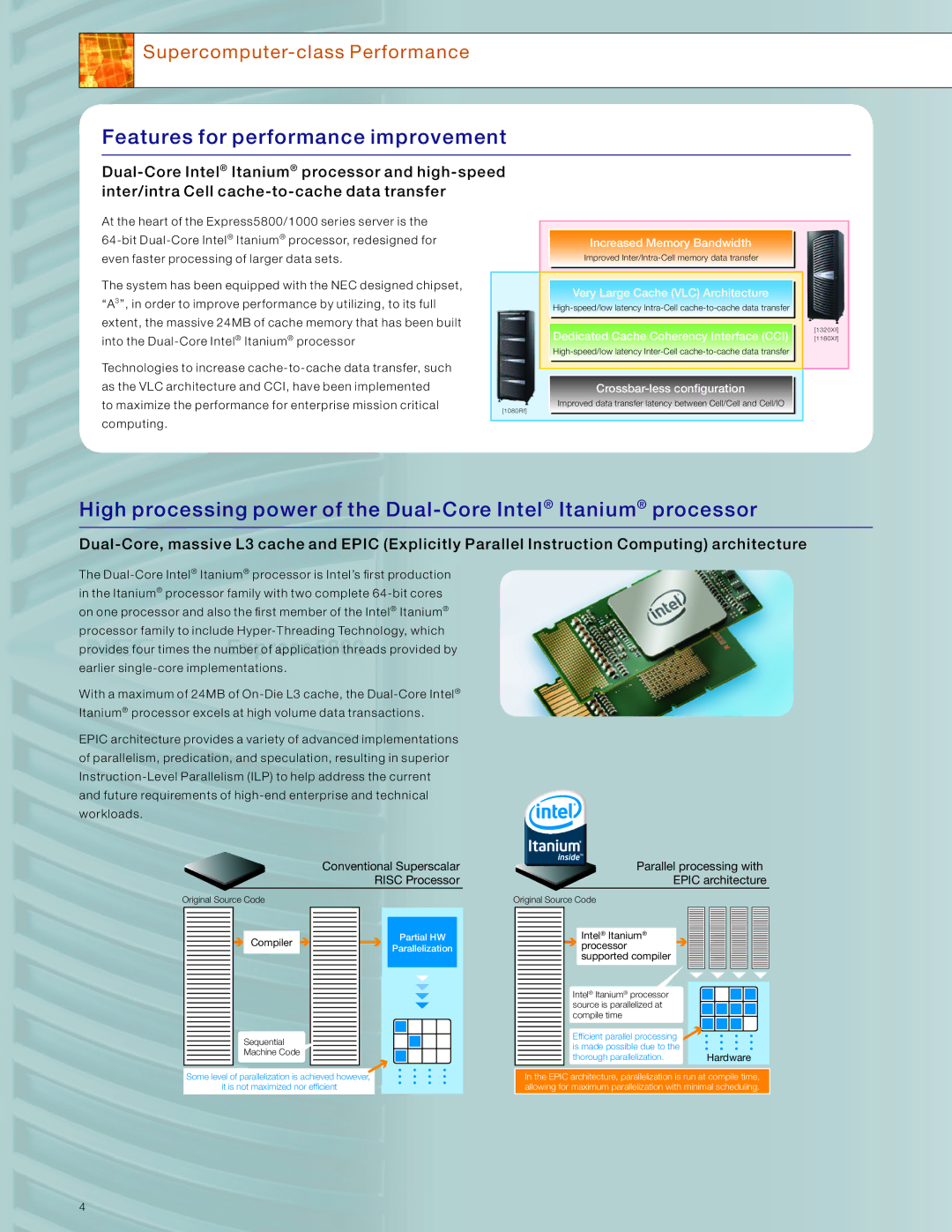

Increased Memory Bandwidth

Improved

Very Large Cache (VLC) Architecture

Dedicated Cache Coherency Interface (CCI)

Improved data transfer latency between Cell/Cell and Cell/IO

[1320Xf]

[1160Xf]

High processing power of the

The

With a maximum of 24MB of

Itanium® processor excels at high volume data transactions.

EPIC architecture provides a variety of advanced implementations of parallelism, predication, and speculation, resulting in superior

Conventional Superscalar RISC Processor

Parallel processing with EPIC architecture

Original Source Code

Compiler

Compiler

Sequential

Machine Code

Some level of parallelization is achieved however, it is not maximized nor efficient

Partial HW

Parallelization

Original Source Code

Intel® Itanium® processor

processor

supported compiler

supported compiler

Intel® Itanium® processor |

|

source is parallelized at |

|

compile time |

|

Efficient parallel processing |

|

is made possible due to the |

|

thorough parallelization. | Hardware |

In the EPIC architecture, parallelization is run at compile time, allowing for maximum parallelization with minimal scheduling.

4