![]()

![]()

PM5347

155 Mb/s SATURN User Network Interface for WANs

FEATURES

• Monolithic |

Asynchronous Transfer Mode (ATM) |

network interface. |

• Implements the ATM transmission |

convergence (TC) sublayer for ATM |

according to ATM Forum specifications |

and |

SONET/SDH 155.52 Mb/s format. Also |

implements ATM Forum specified |

and 12.96 Mb/s. |

• Includes |

clock synthesis at all rates. Clocking |

can be bypassed for use with external |

clock sources. Operates in master or |

slave (loop timed) timing modes. |

• Provides |

outputs. Provides differential pseudo- |

• Supports Fiber Optic, Unshielded |

Twisted Pair and Shielded interfaces. |

• Processes all SONET/SDH UNI |

overhead. |

• Provides access to section and line |

datalinks and all additional transport |

and path overhead to allow additional |

external processing for full SONET/ |

SDH |

compliance. |

TRANSMIT SECTION

•Counts transmit cells read from the transmit FIFO.

•Inserts a register programmable path signal label (C2).

•Inserts path B3, path FEBE indications, line B2, line FEBE indications, and section B1 to allow performance monitoring at the far end.

•Optionally inserts the 16- or

•Optionally inserts an externally generated section user channel (F1), order wire channels (E1, E2) and the DCC channels

•Optionally inserts path AIS, path RDI, line AIS, and line RDI.

•Optionally inserts register programmable APS (K1, K2) and synchronization status (Z1) bytes.

RECEIVE SECTION

•Filters and captures the automatic protection switch channel (K1, K2) bytes in readable registers and detects APS byte failure.

•Extracts the 16- or

•Extracts the DCC channels

•Detects Loss Of Signal (LOS), Out Of Frame (OOF), Loss Of Frame (LOF), line Alarm Indication Signal (AIS), line Remote Defect Indication

•Counts received section B1 errors, line B2 errors, line FEBEs, path B3 errors and path FEBEs for performance monitoring purposes.

APPLICATIONS

•ATM Switching Systems

•ATM Access Systems

•LAN Switches, Hubs and Routers

•ATM Test Equipment

•SONET or SDH ATM Interfaces

• Provides synchronous |

and receive paths with parity support. |

• Inserts and extracts ATM payloads |

using cell delineation. |

• Provides a generic |

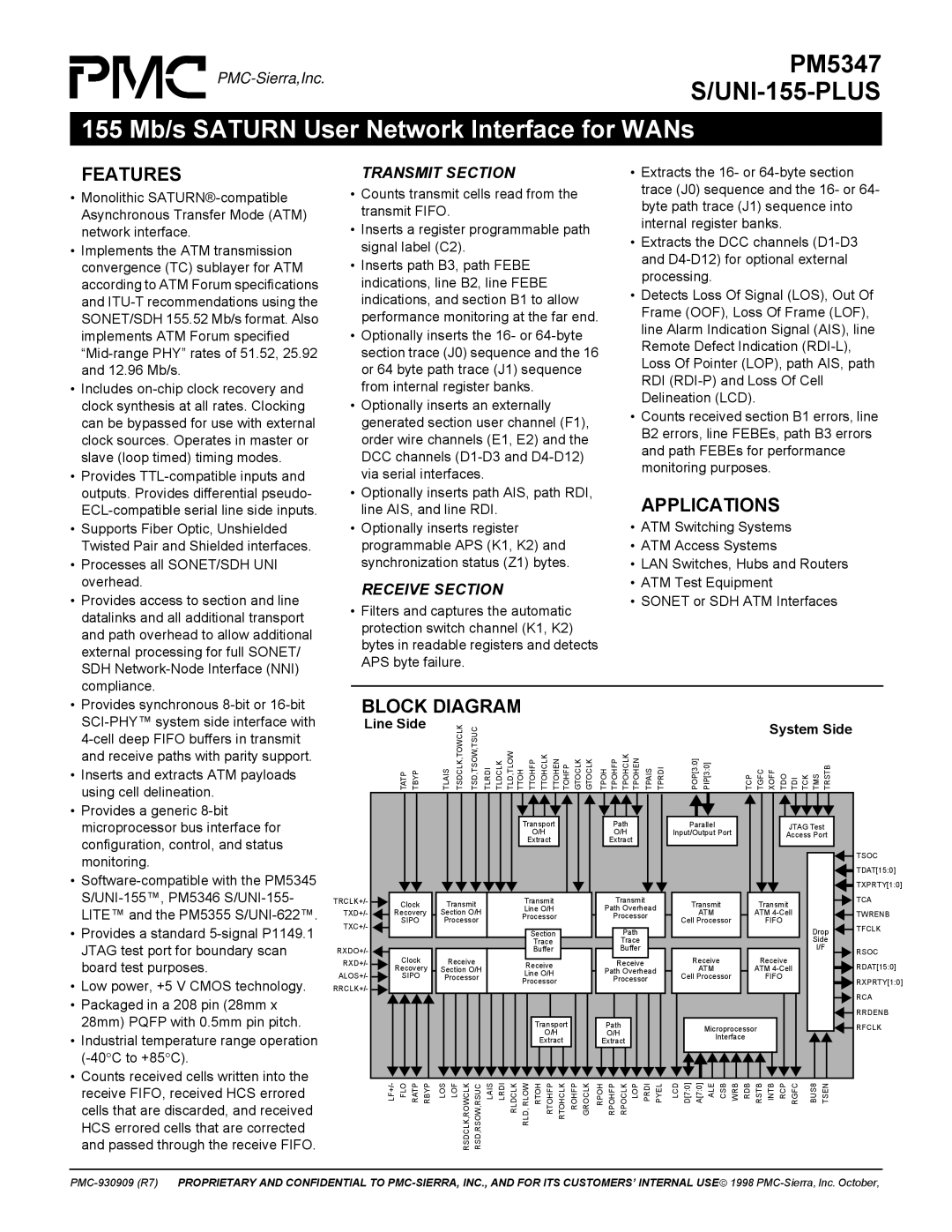

BLOCK DIAGRAM

Line Side | TLAIS TSDCLK,TOWCLK | TSD,TSOW,TSUC TLRDI TLDCLK TLD,TLOW TTOH TTOHFP TTOHCLK TTOHEN TOHFP GTOCLK GTOCLK |

|

|

| System Side |

|

|

|

| |||

TATP TBYP | TPOH TPOHFP POHCLKT TPOHEN TPAIS TPRDI | POP[3:0] PIP[3:0] | TCP TGFC XOFF TDO TDI TCK TMS TRSTB | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

microprocessor bus interface for |

configuration, control, and status |

monitoring. |

• |

LITE™ and the PM5355 |

• Provides a standard |

JTAG test port for boundary scan |

board test purposes. |

• Low power, +5 V CMOS technology. |

• Packaged in a 208 pin (28mm x |

28mm) PQFP with 0.5mm pin pitch. |

• Industrial temperature range operation |

• Counts received cells written into the |

TRCLK+/- ![]() TXD+/-

TXD+/- ![]() TXC+/-

TXC+/- ![]()

RXDO+/- ![]() RXD+/-

RXD+/- ![]() ALOS+/-

ALOS+/- ![]()

RRCLK+/- ![]()

Clock

Recovery

SIPO

Clock

Recovery

SIPO

Transport

O/H

Extract

|

| |

Transmit | Transmit | |

Line O/H | ||

Section O/H | ||

Processor | ||

Processor | ||

|

| Section | |

| Trace | |

| Buffer | |

Receive | Receive | |

Section O/H | ||

Line O/H | ||

Processor | ||

Processor | ||

| ||

| Transport | |

| O/H | |

| Extract |

Path

O/H

Extract

Transmit

Path Overhead

Processor

Path |

Trace |

Buffer |

Receive

Path Overhead

Processor

Path

O/H

Extract

|

|

|

|

| Parallel |

|

|

|

|

|

|

| JTAG Test |

|

|

|

|

|

| |||||||||

|

| Input/Output Port |

|

|

|

|

|

|

| Access Port |

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TSOC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TDAT[15:0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TXPRTY[1:0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TCA |

|

|

|

|

|

| Transmit |

|

|

|

| Transmit |

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

| ATM |

|

|

| ATM |

|

|

|

|

|

|

|

| TWRENB | ||||||||

|

|

| Cell Processor |

|

|

| FIFO |

|

|

|

|

|

|

|

| TFCLK | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Drop |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Side |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| I/F |

|

|

|

| RSOC | ||

|

|

|

|

|

| Receive |

|

|

| Receive |

|

|

|

|

|

|

|

|

|

| RDAT[15:0] | |||||||

|

|

|

|

|

|

| ATM |

|

|

| ATM |

|

|

|

|

|

|

|

|

|

| |||||||

|

|

| Cell Processor |

|

|

| FIFO |

|

|

|

|

|

|

|

|

|

| RXPRTY[1:0] | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RCA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RRDENB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| Microprocessor |

|

|

|

|

|

|

|

|

|

|

|

| RFCLK | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

| Interface |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

receive FIFO, received HCS errored |

cells that are discarded, and received |

HCS errored cells that are corrected |

and passed through the receive FIFO. |

LF+/- FLO RATP RBYP | LOS LOF RSDCLK,ROWCLK RSD,RSOW,RSUC LAIS LRDI RLDCLK RLD, RLOW RTOH RTOHFP RTOHCLK ROHFP GROCLK RPOH RPOHFP RPOCLK LOP PRDI PYEL | LCD D[7:0] A[7:0] ALE CSB WRB RDB RSTB INTB RCP RGFC | BUS8 TSEN |