PM7344

S/UNI-MPH

Quad T1/E1 Multi-PHY SATURN User Network Interface

FEATURES

•Monolithic

•Integrates a quad

•Implements the ATM Forum UNI Specification V3.1 for DS1 and E1 transmission rates.

•Implements the ATM physical layer for Broadband ISDN according to

•Implements direct mapping into four T1 or E1 streams according to

•Provides UTOPIA

•

PM4341A T1XC, PM6341 E1XC, PM4351 COMET, PM5346 S/UNI® - LITE and PM7345

•

•Provides a generic

microprocessor bus interface for configuration, control, and status monitoring.

•Low power, +5 V, CMOS technology.

•Packaged in a

(14 mm by 20 mm) PQFP package.

T1 FRAMER/TRANSMITTER

•Supports SF or ESF format signals using B8ZS or AMI line code.

•Provides Loss Of Signal (LOS) detection and red, yellow and Alarm Indication Signal (AIS) alarm detection. Supports transmission of (AIS) or yellow alarm signal in all formats.

•Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving

•Supports line and path performance monitoring according to ANSI specifications. Accumulators are provided for counting ESF

•Provides ESF

•Extracts/inserts the datalink in ESF mode.

E1 FRAMER/TRANSMITTER

•Supports G.704 2048 kbit/s format using HDB3 or AMI line coding.

•Supports CRC multiframe alignment or the signalling multiframe alignment.

•Declares red and AIS alarms using Q.516 recommended integration periods. Provides LOS detection, and indicates loss of frame alignment (OOF), loss of signalling, and loss of CRC multiframe alignment.

•Supports line and path performance monitoring according to

•Supports reception and transmission of remote alarm and AIS.

•Provides an HDLC interface for terminating/generating a datalink.

•Supports the timeslot 16 (64 kbit/s) datalink which may be used for common channel signalling, or any combination of the national bits.

APPLICATIONS

•ATM Switches Supporting DS1 or E1 UNI Ports

•ATM Switches Supporting DS3 or E3 Ports Carrying Multiplexed DS1 or E1 UNI Signals

•ATM Switches Supporting SONET/ SDH Ports Carrying Tributary Mapped DS1 or E1 UNI Signals

•ATM Customer Premise Equipment Supporting Multiple DS1 or E1 UNI Ports

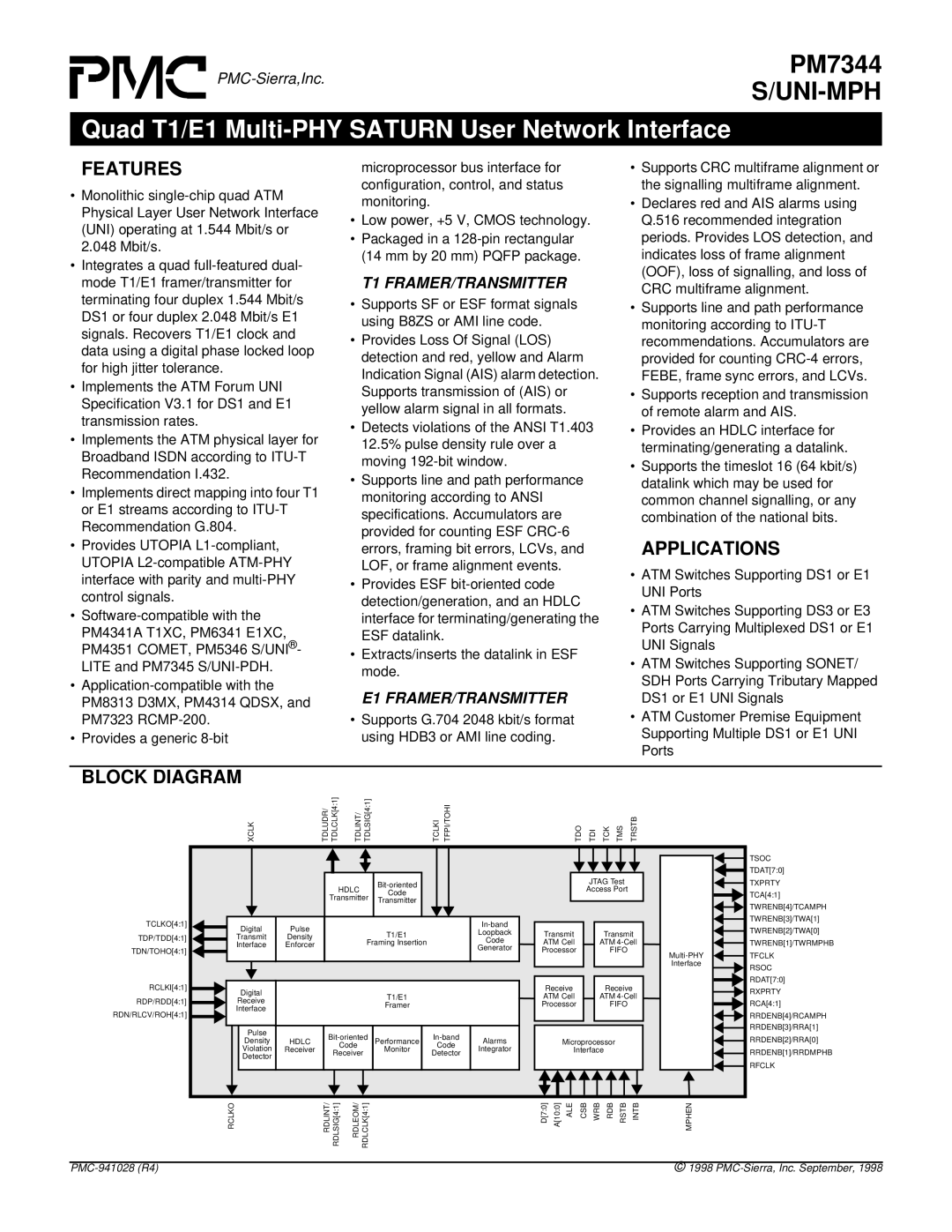

BLOCK DIAGRAM

|

|

|

|

|

| XCLK |

|

| TDLUDR/ | TDLCLK[4:1] | TDLINT/ | TDLSIG[4:1] |

|

| TCLKI TFPI/TOHI |

|

|

|

|

|

|

|

|

|

|

| TDO | TDI | TCK | TMS | TRSTB |

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TSOC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TDAT[7:0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| JTAG Test |

|

|

|

|

|

| TXPRTY | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| HDLC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Access Port |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Code |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TCA[4:1] | ||||||||

|

|

|

|

|

|

|

|

|

|

|

| Transmitter |

|

| Transmitter |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TWRENB[4]/TCAMPH |

TCLKO[4:1] |

|

|

|

| Digital |

|

| Pulse |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TWRENB[3]/TWA[1] | |||

|

|

|

|

|

|

|

|

|

|

|

| T1/E1 |

|

|

|

| Loopback |

|

|

|

| Transmit |

|

|

| Transmit |

|

|

|

|

|

| TWRENB[2]/TWA[0] | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

TDP/TDD[4:1] |

|

|

| Transmit |

|

| Density |

|

|

| Framing Insertion |

|

|

|

| Code |

|

|

|

| ATM Cell |

|

|

| ATM |

|

|

|

|

|

| TWRENB[1]/TWRMPHB | ||||||||||||||

|

|

|

| Interface |

|

| Enforcer |

|

|

|

|

|

|

| Generator |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

TDN/TOHO[4:1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Processor |

|

|

|

| FIFO |

|

|

|

|

| TFCLK | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Interface |

| RSOC | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

RCLKI[4:1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Receive |

|

|

| Receive |

|

|

|

|

|

| RDAT[7:0] | ||||||||

|

|

|

| Digital |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXPRTY | |||||||||||||

RDP/RDD[4:1] |

|

|

| Receive |

|

|

|

|

|

|

|

| T1/E1 |

|

|

|

|

|

|

|

|

| ATM Cell |

|

|

| ATM |

|

|

|

|

|

| RCA[4:1] | ||||||||||||

|

|

|

| Interface |

|

|

|

|

|

|

|

| Framer |

|

|

|

|

|

|

|

| Processor |

|

|

|

| FIFO |

|

|

|

|

|

| |||||||||||||

RDN/RLCV/ROH[4:1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RRDENB[4]/RCAMPH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RRDENB[3]/RRA[1] |

|

|

|

|

|

| Pulse |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RRDENB[2]/RRA[0] | |||||||

|

|

|

|

|

| Density |

|

| HDLC |

| Performance |

|

|

| Alarms |

|

|

|

|

|

|

| Microprocessor |

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

| Violation |

|

| Receiver |

|

| Code |

|

| Monitor |

| Code |

|

| Integrator |

|

|

|

|

|

|

|

|

| Interface |

|

|

|

|

|

|

|

| RRDENB[1]/RRDMPHB | |||||||

|

|

|

|

|

| Detector |

|

|

|

| Receiver |

|

|

| Detector |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RFCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RCLKO |

|

| RDLINT/ | RDLSIG[4:1] | RDLEOM/ | RDLCLK[4:1] |

|

|

|

|

|

|

|

|

|

| D[7:0] | A[10:0] ALE | CSB |

| WRB |

| RDB | RSTB | INTB |

| MPHEN |

| ||||||||||||||

© 1998 |