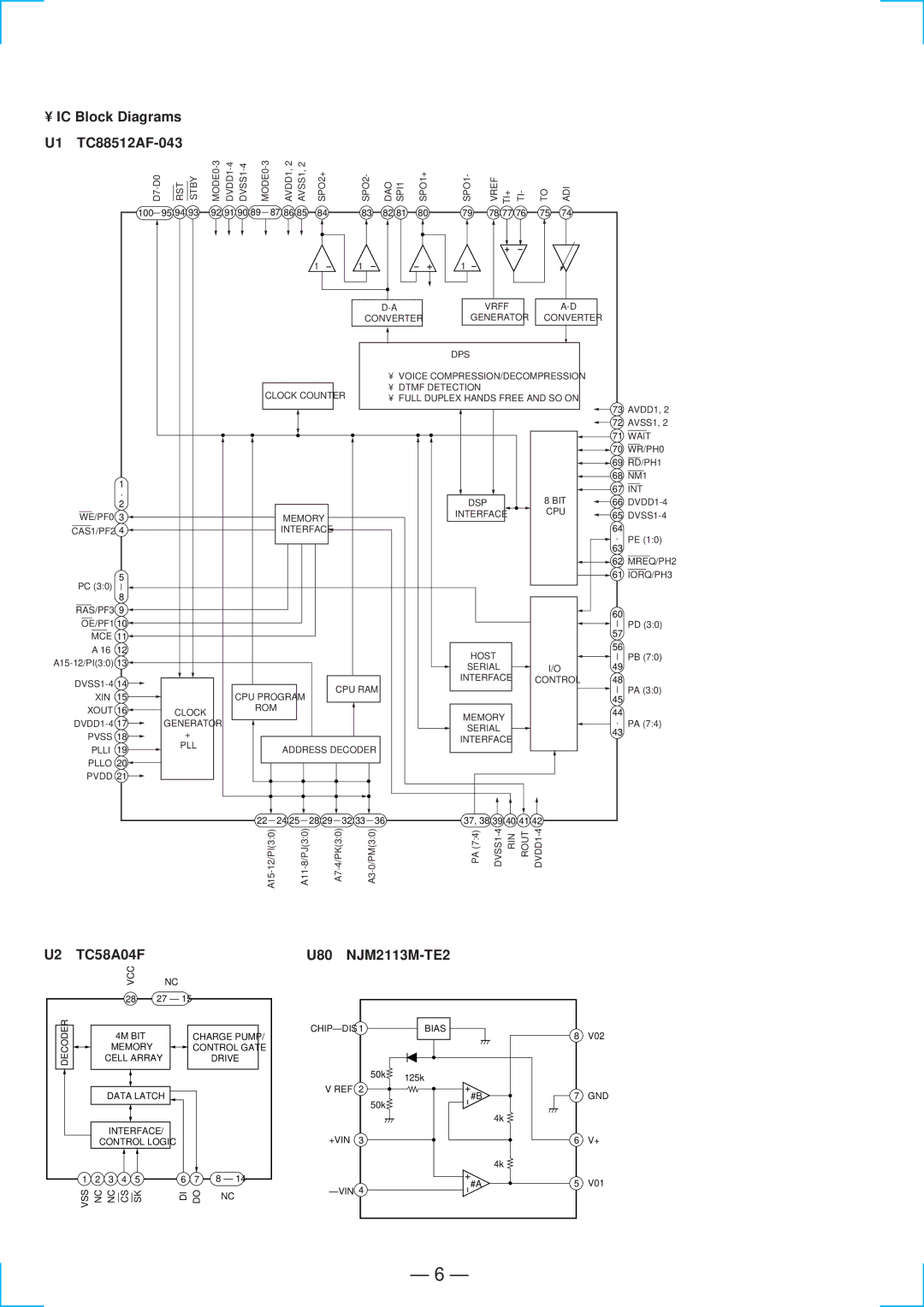

• IC Block Diagrams

U1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| RST STBY | AVDD1, 2 AVSS1, 2 | SPO2+ |

| SPO2- | DAO SPI1 | SPO1+ | SPO1- | VREF TI+ | TI- | TO | ADI |

|

| |||||

|

| 100 | 95 94 93 | 92 91 90 89 | 87 86 85 | 84 |

| 83 | 82 81 | 80 | 79 | 78 77 76 | 75 | 74 |

|

| ||||

|

|

|

|

|

|

|

|

| 1 |

| 1 |

|

| 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VRFF |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| CONVERTER |

| GENERATOR | CONVERTER |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| DPS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| • VOICE COMPRESSION/DECOMPRESSION |

|

|

| |||||

|

|

|

|

|

|

| CLOCK COUNTER |

|

| • DTMF DETECTION |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| • FULL DUPLEX HANDS FREE AND SO ON |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 73 | AVDD1, 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 72 | AVSS1, 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 71 | WAIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 70 | WR/PH0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 69 | RD/PH1 |

|

| 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 68 | NM1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 67 | INT | |

|

| . |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| DSP |

|

| 8 BIT | 66 | |||

|

| 2 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| WE/PF0 | 3 |

|

|

|

|

| MEMORY |

|

|

|

| INTERFACE |

| CPU | 65 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| CAS1/PF2 | 4 |

|

|

|

|

| INTERFACE |

|

|

|

|

|

|

|

|

| 64 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| . | PE (1:0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 63 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 62 | MREQ/PH2 |

| PC (3:0) | 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 61 | IORQ/PH3 |

| 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| RAS/PF3 | 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 60 |

|

| OE/PF1 | 10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PD (3:0) | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 57 | |||

| MCE | 11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| A 16 | 12 |

|

|

|

|

|

|

|

|

|

|

| HOST |

|

|

| 56 | PB (7:0) | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 49 | |||||

|

|

|

|

|

|

|

|

|

|

| SERIAL |

| I/O |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 14 |

|

|

|

|

|

|

| CPU RAM |

|

| INTERFACE |

| CONTROL | 48 | PA (3:0) | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| XIN | 15 |

|

|

| CPU PROGRAM |

|

|

|

|

|

|

|

| 45 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| XOUT | 16 | CLOCK |

|

| ROM |

|

|

|

|

|

| MEMORY |

|

|

| 44 |

| ||

| 17 | GENERATOR |

|

|

|

|

|

|

|

|

|

|

|

|

| . | PA (7:4) | |||

|

|

|

|

|

|

|

|

|

|

| SERIAL |

|

|

| ||||||

| PVSS | 18 | + |

|

|

|

|

|

|

|

|

|

|

|

|

| 43 |

| ||

|

|

|

|

|

|

|

|

|

|

| INTERFACE |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| PLLI | 19 | PLL |

|

|

|

| ADDRESS DECODER |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| PLLO | 20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PVDD | 21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 22 | 24 25 | 28 29 |

| 32 33 | 36 |

| 37, 38 | 39 40 41 42 |

|

|

| |||

|

|

|

|

|

|

|

|

|

| PA (7:4) | ROUT |

|

|

| ||||||

U2 | TC58A04F |

|

|

| ||||

|

|

|

| VCC |

| NC |

|

|

|

|

|

| 28 | 27 – 15 |

|

| |

DECODER |

|

|

| 4M BIT |

| CHARGE PUMP/ | ||

|

| MEMORY |

| CONTROL GATE | ||||

|

| CELL ARRAY |

|

| DRIVE | |||

|

|

|

|

|

|

|

| |

|

|

| DATA LATCH |

|

|

| ||

|

|

| INTERFACE/ |

|

|

| ||

|

| CONTROL LOGIC |

|

| ||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 – 14 |

| VSS | NC | NC | CS | SK | DI | DO | NC |

|

| |||||||

U80 |

|

|

| |||

1 |

| BIAS | 8 | V02 | ||

|

|

|

|

| ||

|

|

| 50k | 125k |

|

|

|

|

|

|

|

| |

V REF | 2 |

| #B | 7 | GND | |

|

|

| 50k | |||

|

|

|

|

|

| |

|

|

|

|

| 4k |

|

+VIN | 3 |

|

| 6 | V+ | |

|

|

|

|

| 4k |

|

4 |

| #A | 5 | V01 | ||

|

|

|

| |||

|

|

|

| – 6 – |

|

|