TAS5518 specifications

Texas Instruments TAS5518 is a highly integrated audio amplifier designed to deliver superior sound quality and efficient power management for a variety of applications. This device is particularly well-suited for use in consumer electronics, including televisions, soundbars, and wireless audio systems. One of the standout features of the TAS5518 is its ability to provide a high level of audio fidelity while integrating seamlessly into compact designs.At the heart of the TAS5518 is its advanced digital signal processing (DSP) technology. This allows for precise audio management, enabling the amplifier to optimize sound quality across different playback scenarios. With built-in equalization and dynamic range compression, the TAS5518 can enhance audio output by automatically adjusting the sound profile to suit the content. This results in a more immersive listening experience, whether users are watching movies or listening to music.

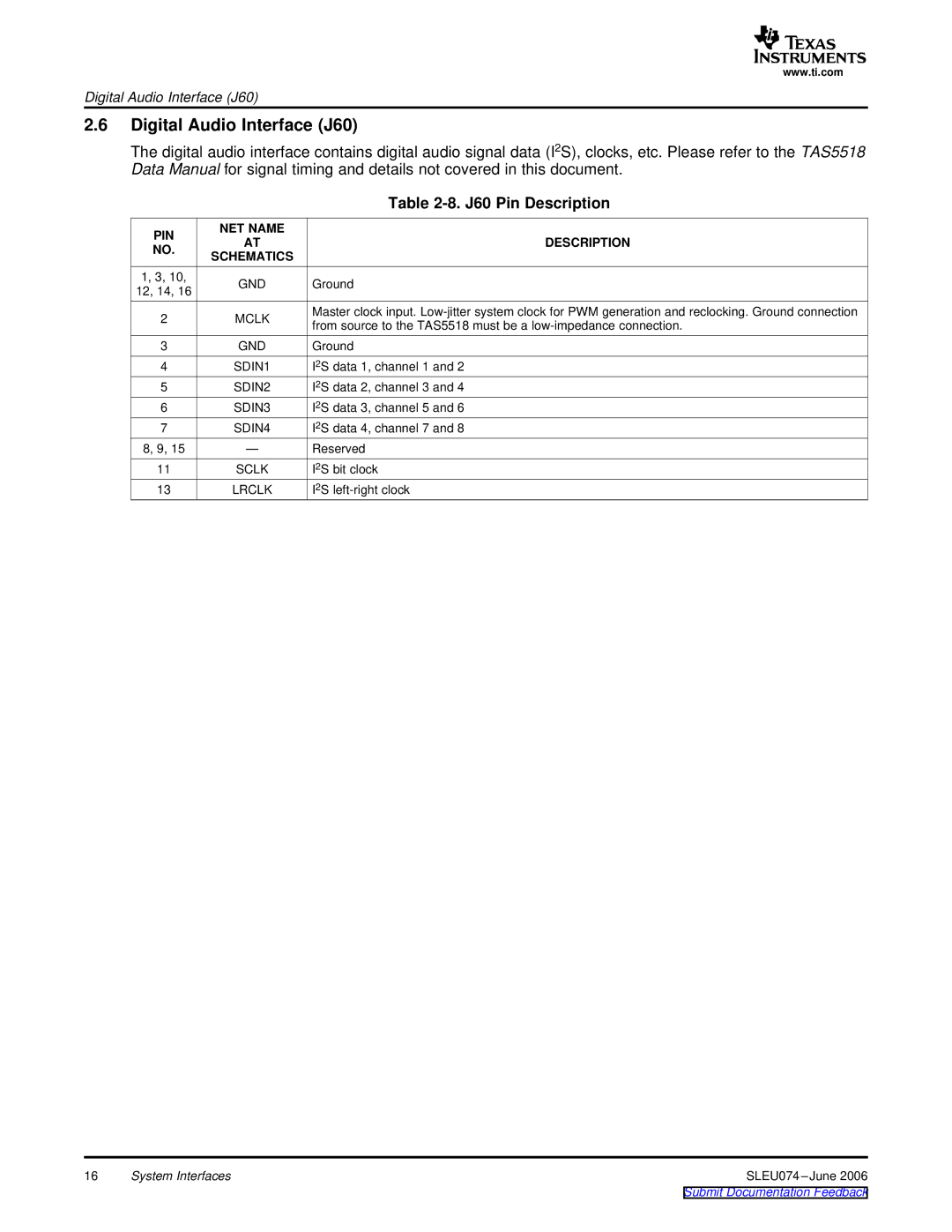

The TAS5518 is equipped with multiple channels, offering up to 8 channels of output. This feature makes it an ideal choice for multi-channel audio applications, where immersive sound is paramount. The device supports various speaker configurations, allowing designers the flexibility to create customized setups that meet the specific needs of their products.

In terms of power management, the TAS5518 incorporates various technologies aimed at improving efficiency. It features a class-D amplifier architecture, which not only minimizes power consumption but also reduces heat generation. This efficient operation contributes to longer battery life in portable devices and lower energy costs in stationary applications.

Another key characteristic of the TAS5518 is its compatibility with high-resolution audio formats. This ensures that the amplifier can reproduce high-quality audio with excellent clarity and accuracy. Additionally, the TAS5518 supports various input formats, making it versatile for a wide range of audio sources.

On the connectivity front, it offers digital interfaces that make integration with other components straightforward. This capability allows for simplified design and reduced development time for engineers working on audio solutions.

Overall, the Texas Instruments TAS5518 is a compelling choice for engineers seeking to enhance audio performance in their products. With its focus on audio precision, power efficiency, and versatility, it stands out as a valuable component in modern audio systems. Its combination of features and characteristics ensures that end users enjoy a high-fidelity audio experience across different applications.