| |

| |

| |

| |

2.5” Solid State Disk | |

|

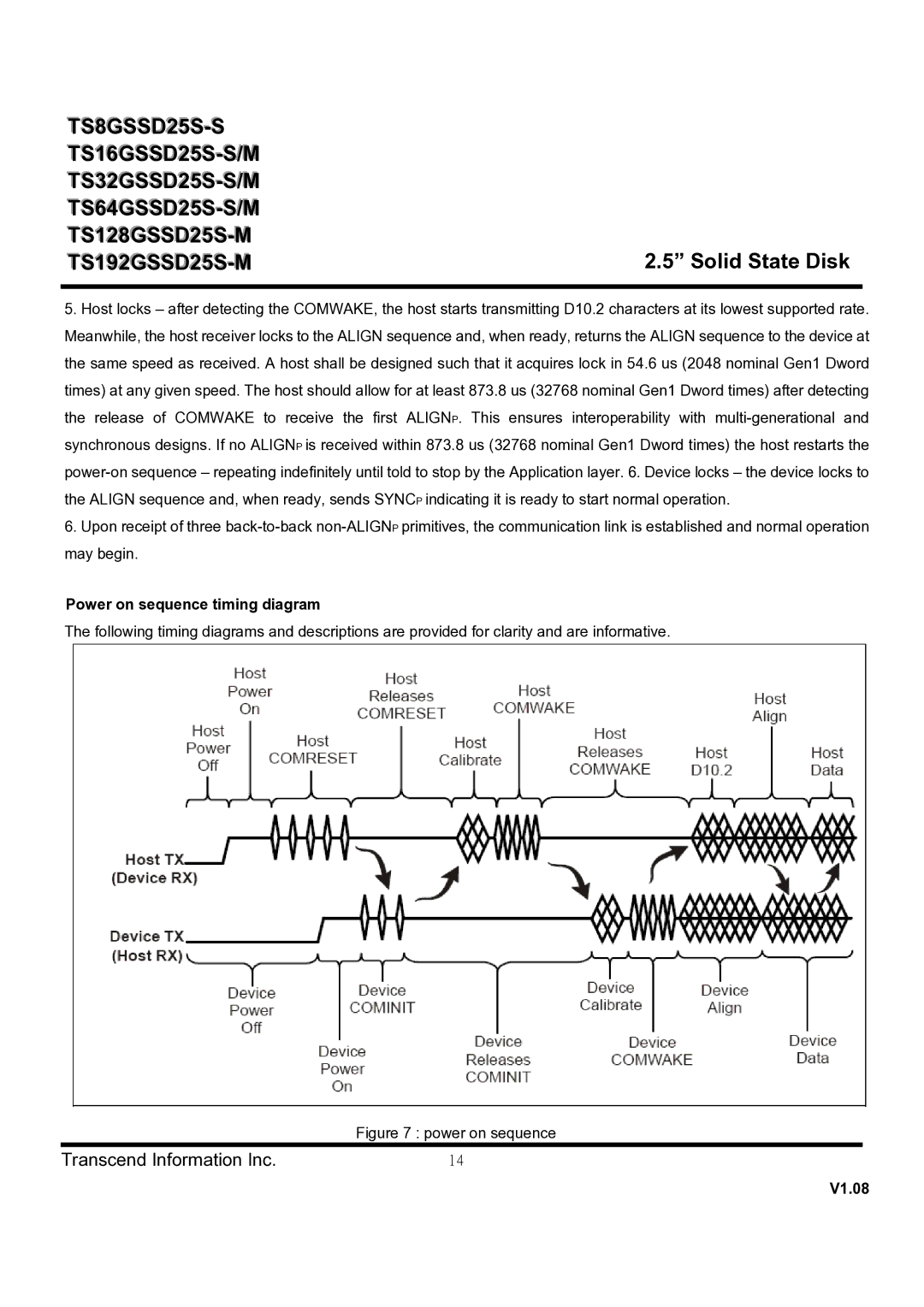

5.Host locks – after detecting the COMWAKE, the host starts transmitting D10.2 characters at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6 us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGNP. This ensures interoperability with

6.Upon receipt of three

Power on sequence timing diagram

The following timing diagrams and descriptions are provided for clarity and are informative.

| Figure 7 : power on sequence |

Transcend Information Inc. | 14 |