White Paper | 14 |

PowerPC G5

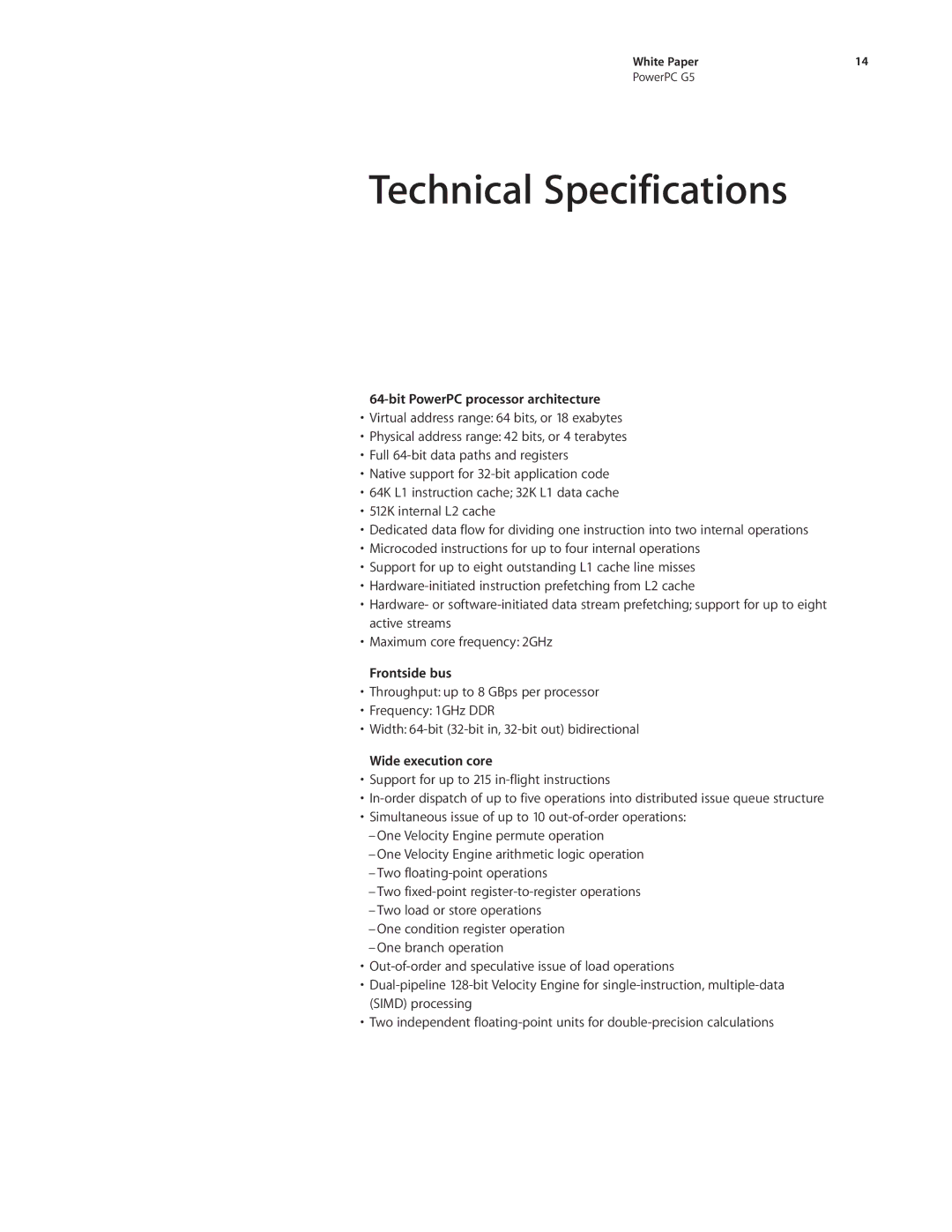

Technical Specifications

64-bit PowerPC processor architecture

•Virtual address range: 64 bits, or 18 exabytes

•Physical address range: 42 bits, or 4 terabytes

•Full

•Native support for

•64K L1 instruction cache; 32K L1 data cache

•512K internal L2 cache

•Dedicated data flow for dividing one instruction into two internal operations

•Microcoded instructions for up to four internal operations

•Support for up to eight outstanding L1 cache line misses

•

•Hardware- or

•Maximum core frequency: 2GHz

Frontside bus

•Throughput: up to 8 GBps per processor

•Frequency: 1GHz DDR

•Width:

Wide execution core

•Support for up to 215

•

•Simultaneous issue of up to 10

–One Velocity Engine permute operation

–One Velocity Engine arithmetic logic operation

–Two

–Two

–Two load or store operations

–One condition register operation

–One branch operation

•

•

•Two independent