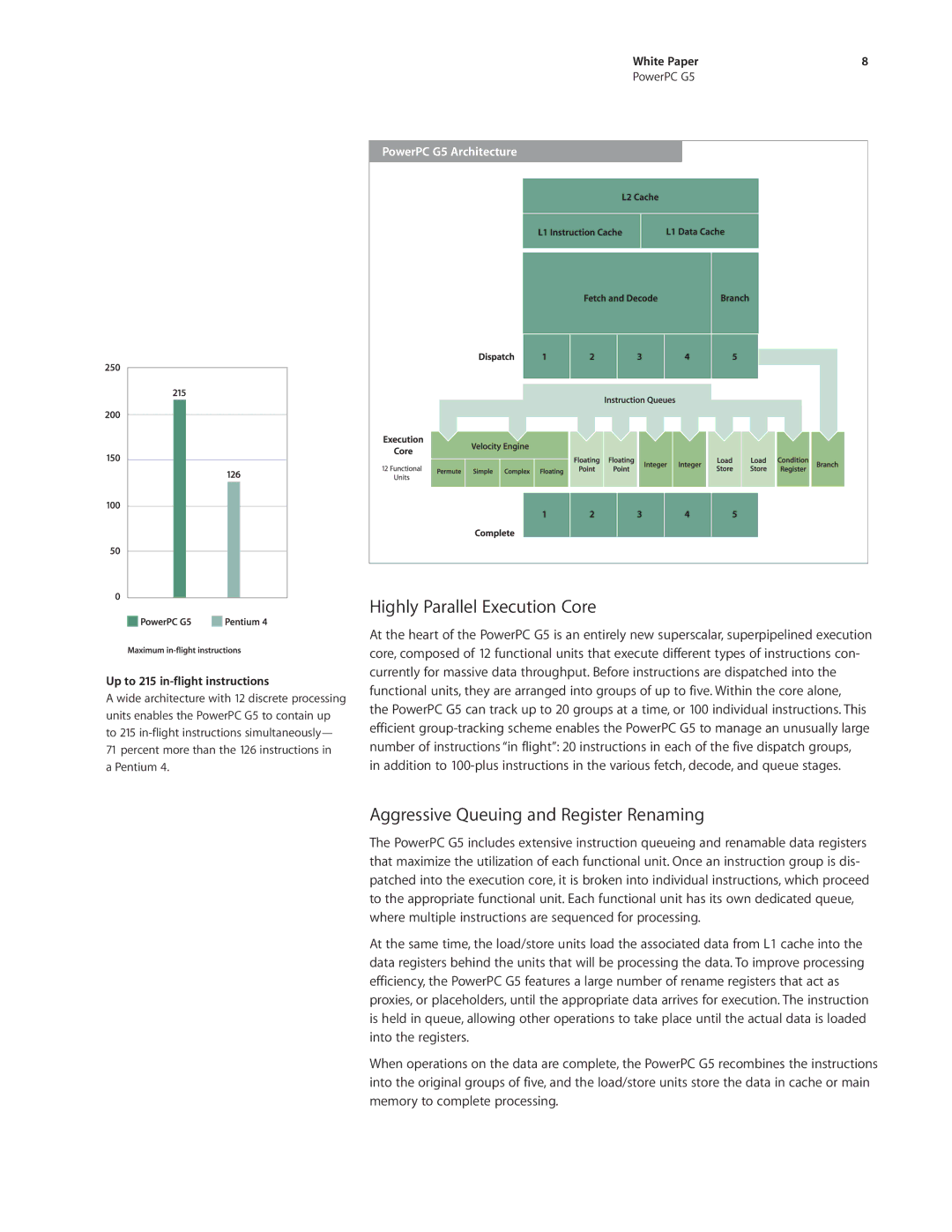

Up to 215 in-flight instructions

A wide architecture with 12 discrete processing units enables the PowerPC G5 to contain up to 215

White Paper | 8 |

PowerPC G5

PowerPC G5 Architecture

Highly Parallel Execution Core

At the heart of the PowerPC G5 is an entirely new superscalar, superpipelined execution core, composed of 12 functional units that execute different types of instructions con- currently for massive data throughput. Before instructions are dispatched into the functional units, they are arranged into groups of up to five. Within the core alone, the PowerPC G5 can track up to 20 groups at a time, or 100 individual instructions. This efficient

Aggressive Queuing and Register Renaming

The PowerPC G5 includes extensive instruction queueing and renamable data registers that maximize the utilization of each functional unit. Once an instruction group is dis- patched into the execution core, it is broken into individual instructions, which proceed to the appropriate functional unit. Each functional unit has its own dedicated queue, where multiple instructions are sequenced for processing.

At the same time, the load/store units load the associated data from L1 cache into the data registers behind the units that will be processing the data. To improve processing efficiency, the PowerPC G5 features a large number of rename registers that act as proxies, or placeholders, until the appropriate data arrives for execution. The instruction is held in queue, allowing other operations to take place until the actual data is loaded into the registers.

When operations on the data are complete, the PowerPC G5 recombines the instructions into the original groups of five, and the load/store units store the data in cache or main memory to complete processing.