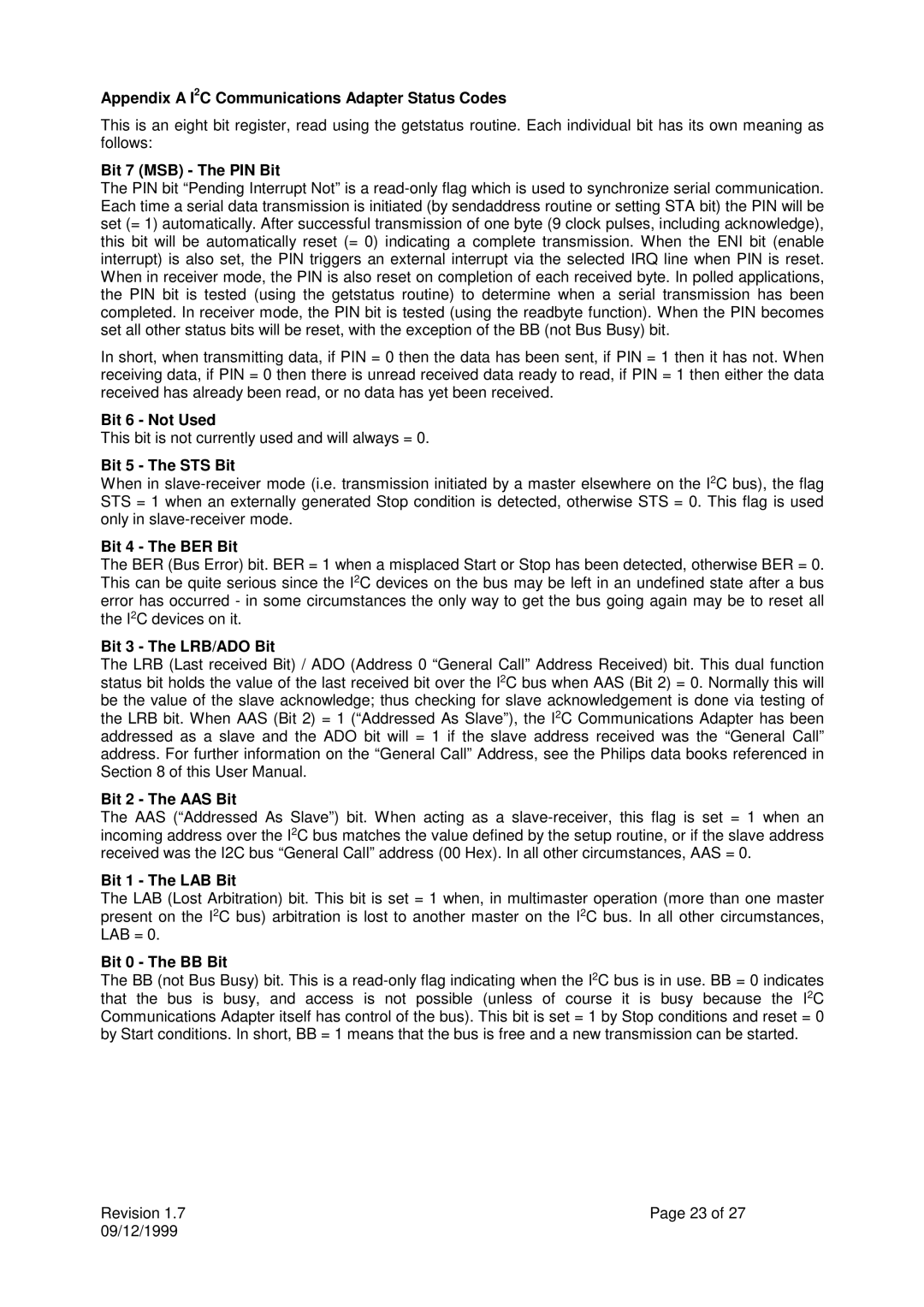

Appendix A I2C Communications Adapter Status Codes

This is an eight bit register, read using the getstatus routine. Each individual bit has its own meaning as follows:

Bit 7 (MSB) - The PIN Bit

The PIN bit “Pending Interrupt Not” is a

In short, when transmitting data, if PIN = 0 then the data has been sent, if PIN = 1 then it has not. When receiving data, if PIN = 0 then there is unread received data ready to read, if PIN = 1 then either the data received has already been read, or no data has yet been received.

Bit 6 - Not Used

This bit is not currently used and will always = 0.

Bit 5 - The STS Bit

When in

Bit 4 - The BER Bit

The BER (Bus Error) bit. BER = 1 when a misplaced Start or Stop has been detected, otherwise BER = 0. This can be quite serious since the I2C devices on the bus may be left in an undefined state after a bus error has occurred - in some circumstances the only way to get the bus going again may be to reset all the I2C devices on it.

Bit 3 - The LRB/ADO Bit

The LRB (Last received Bit) / ADO (Address 0 “General Call” Address Received) bit. This dual function status bit holds the value of the last received bit over the I2C bus when AAS (Bit 2) = 0. Normally this will be the value of the slave acknowledge; thus checking for slave acknowledgement is done via testing of the LRB bit. When AAS (Bit 2) = 1 (“Addressed As Slave”), the I2C Communications Adapter has been addressed as a slave and the ADO bit will = 1 if the slave address received was the “General Call” address. For further information on the “General Call” Address, see the Philips data books referenced in Section 8 of this User Manual.

Bit 2 - The AAS Bit

The AAS (“Addressed As Slave”) bit. When acting as a

Bit 1 - The LAB Bit

The LAB (Lost Arbitration) bit. This bit is set = 1 when, in multimaster operation (more than one master present on the I2C bus) arbitration is lost to another master on the I2C bus. In all other circumstances, LAB = 0.

Bit 0 - The BB Bit

The BB (not Bus Busy) bit. This is a

Revision 1.7 | Page 23 of 27 |

09/12/1999 |

|