XRD9829REF

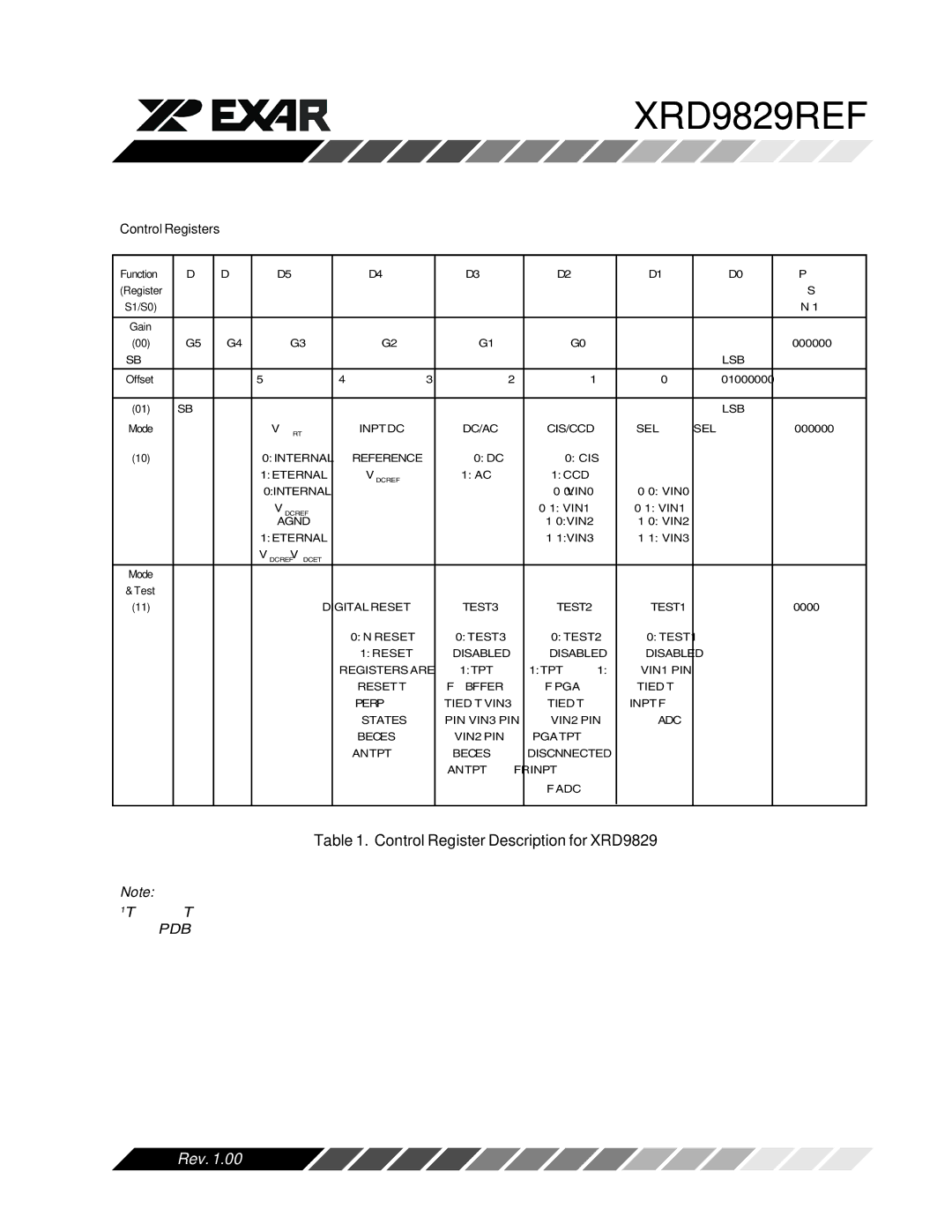

Control Registers

Function | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

(Register |

|

|

|

|

|

|

|

| State |

S1/S0) |

|

|

|

|

|

|

|

| (Note 1) |

|

|

|

|

|

|

|

|

|

|

Gain |

|

|

|

|

|

|

|

|

|

(00) | G5 | G4 | G3 | G2 | G1 | G0 | X | X | 000000XX |

(MSB) |

|

|

|

|

|

|

| (LSB) |

|

|

|

|

|

|

|

|

|

|

|

Offset | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 | 01000000 |

|

|

|

|

|

|

|

|

|

|

(01) | (MSB) |

|

|

|

|

|

| (LSB) |

|

Mode | X | X | VRT | INPUTDC | DC/AC | CIS/CCD | MUX SEL | MUX SEL | XX000000 |

(10) |

|

| 0: INTERNAL | REFERENCE | 0: DC | 0: CIS |

|

|

|

|

|

| 1: EXTERNAL | (VDCREF) | 1: AC | 1: CCD |

|

|

|

|

|

| 0:INTERNAL |

|

| 0 0: VIN0 | 0 0: VIN0 |

|

|

|

|

| (VDCREF= |

|

| 0 1: VIN1 | 0 1: VIN1 |

|

|

|

|

| AGND) |

|

| 1 0: VIN2 | 1 0: VIN2 |

|

|

|

|

| 1: EXTERNAL |

|

| 1 1: VIN3 | 1 1: VIN3 |

|

|

|

|

| (VDCREF=VDCEXT) |

|

|

|

|

|

|

Mode |

|

|

|

|

|

|

|

|

|

& Test |

|

|

|

|

|

|

|

|

|

(11) | X | X | X | DIGITAL RESET | TEST3 | TEST2 | TEST1 | X | XXX0000X |

|

|

|

| 0: NO RESET | 0: TEST3 | 0: TEST2 | 0: TEST1 |

|

|

|

|

|

| 1: RESET | DISABLED | DISABLED | DISABLED |

|

|

|

|

|

| (REGISTERS ARE | 1: OUTPUT | 1: OUTPUT | 1: VIN1 PIN |

|

|

|

|

|

| RESETTO | OFBUFFER | OF PGA | TIED TO |

|

|

|

|

|

| TIED TO VIN3 | TIED TO | INPUT OF |

|

| |

|

|

|

| STATES) | PIN (VIN3 PIN | VIN2 PIN | ADC |

|

|

|

|

|

| BECOMES | (VIN2 PIN | (PGA OUTPUT |

|

|

|

|

|

|

| ANOUTPUT) | BECOMES | DISCONNECTED |

|

|

|

|

|

|

|

| ANOUTPUT) | FROMINPUT |

|

|

|

|

|

|

|

|

| OFADC) |

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 1. Control Register Description for XRD9829

Note:

1These are the control register settings upon initial

Rev. 1.00

7