Pin No. | Terminal | In/Out | Function | |

93 | VCC5 | In | +5V source | |

|

|

|

| |

94, 95 |

|

|

| |

97 ~ 105 | EA0 ~ EA14 | Out | Address bus for the effect RAM | |

107,109 | ||||

|

|

| ||

110, 112 |

|

|

| |

|

|

|

| |

96 | EWEB | Out | Write enable signal output for the effect RAM | |

|

|

|

| |

106 | EOEB | Out | Read enable signal output for the effect RAM | |

|

|

|

| |

108 | VCC7 | In | +5V source | |

|

|

|

| |

111 | ECEB | Out | Chip select signal output for the effect RAM | |

|

|

|

| |

113 ~ 117 |

|

| Not used. | |

|

|

|

| |

118 | VCC4 | In | +5V source | |

|

|

|

| |

119 | GND4 | In | Ground (0V) source | |

|

|

|

| |

120 ~ 122 |

|

| Not sued. | |

|

|

|

| |

123 ~ 130 | ED0 ~ ED7 | In/Out | Data bus for the effect RAM | |

|

|

|

| |

131 | GND5 | In | Ground (0V) source | |

|

|

|

| |

132 ~ 134 |

|

| Not used. Connected to ground. | |

|

|

|

| |

135, 136 |

|

| Not used. | |

|

|

|

|

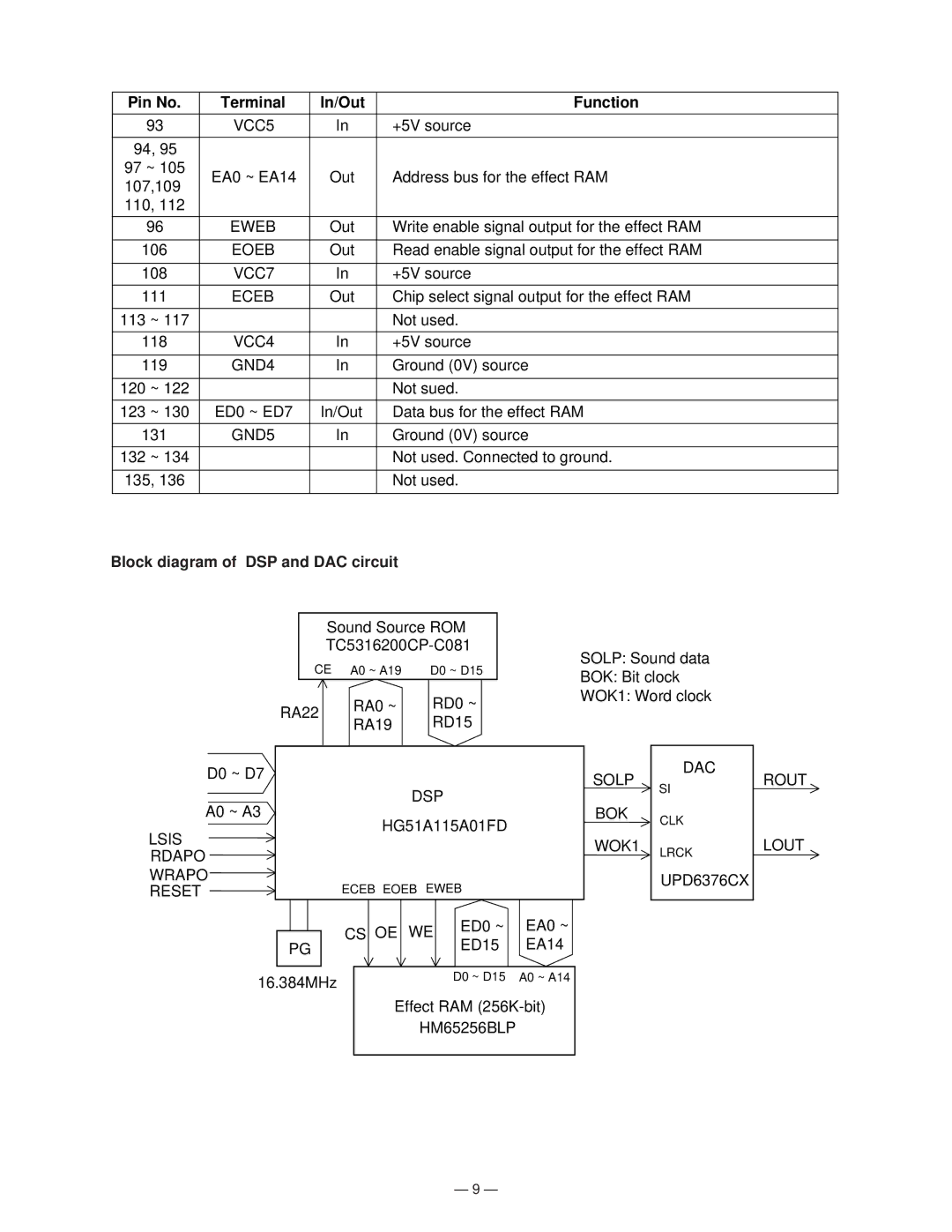

Block diagram of DSP and DAC circuit

|

| Sound Source ROM | ||

|

| |||

| CE A0 ~ A19 | D0 ~ D15 | ||

RA22 | RA0 ~ | RD0 ~ | ||

RA19 | RD15 | |||

|

| |||

SOLP: Sound data

BOK: Bit clock

WOK1: Word clock

D0 ~ D7 |

|

|

|

|

|

|

|

|

|

|

A0 ~ A3 |

|

|

|

|

|

| DSP |

|

|

|

|

|

|

|

|

| HG51A115A01FD |

|

| ||

LSIS |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| |

RDAPO |

|

|

|

|

|

|

|

|

|

|

WRAPO |

|

|

|

| ECEB EOEB EWEB |

|

| |||

RESET |

|

|

|

|

|

| ||||

|

|

|

|

| CS | OE WE | ED0 ~ | EA0 ~ |

| |

| PG |

| ED15 | EA14 |

| |||||

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

16.384MHz |

|

|

| D0 ~ D15 | A0 ~ A14 |

| ||||

|

|

|

|

|

| |||||

|

|

|

|

|

|

| Effect RAM |

| ||

|

|

|

|

|

|

| HM65256BLP |

|

| |

|

|

|

|

|

|

|

|

|

|

|

SOLP

BOK

WOK1

DAC

SI

CLK

LRCK

UPD6376CX

ROUT

LOUT

— 9 —