BIOS Overview

PCI Interrupt Request Lines

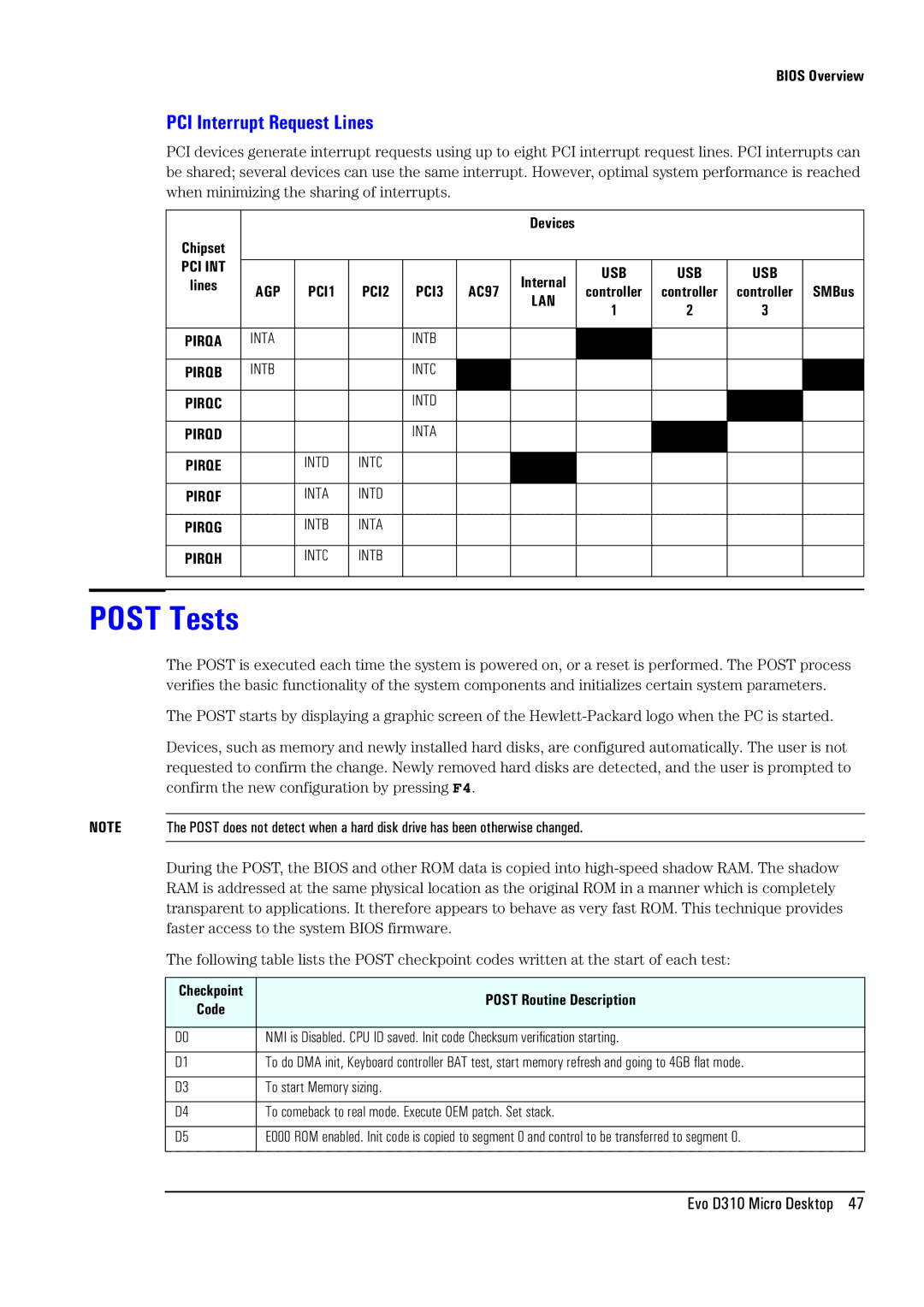

PCI devices generate interrupt requests using up to eight PCI interrupt request lines. PCI interrupts can be shared; several devices can use the same interrupt. However, optimal system performance is reached when minimizing the sharing of interrupts.

|

|

|

|

|

|

| Devices |

|

|

|

|

| Chipset |

|

|

|

|

|

|

|

|

|

|

| PCI INT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Internal | USB | USB | USB |

| |

| lines |

|

|

|

|

|

| ||||

| AGP | PCI1 | PCI2 | PCI3 | AC97 | controller | controller | controller | SMBus | ||

|

| LAN | |||||||||

|

|

|

|

|

|

| 1 | 2 | 3 |

| |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQA | INTA |

|

| INTB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQB | INTB |

|

| INTC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQC |

|

|

| INTD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQD |

|

|

| INTA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQE |

| INTD | INTC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQF |

| INTA | INTD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQG |

| INTB | INTA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PIRQH |

| INTC | INTB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST Tests

The POST is executed each time the system is powered on, or a reset is performed. The POST process verifies the basic functionality of the system components and initializes certain system parameters.

The POST starts by displaying a graphic screen of the

Devices, such as memory and newly installed hard disks, are configured automatically. The user is not requested to confirm the change. Newly removed hard disks are detected, and the user is prompted to confirm the new configuration by pressing F4.

NOTE The POST does not detect when a hard disk drive has been otherwise changed.

During the POST, the BIOS and other ROM data is copied into

The following table lists the POST checkpoint codes written at the start of each test:

Checkpoint | POST Routine Description | |

Code | ||

| ||

|

| |

D0 | NMI is Disabled. CPU ID saved. Init code Checksum verification starting. | |

|

| |

D1 | To do DMA init, Keyboard controller BAT test, start memory refresh and going to 4GB flat mode. | |

|

| |

D3 | To start Memory sizing. | |

|

| |

D4 | To comeback to real mode. Execute OEM patch. Set stack. | |

|

| |

D5 | E000 ROM enabled. Init code is copied to segment 0 and control to be transferred to segment 0. | |

|

|

Evo D310 Micro Desktop 47