130nm node CMOS Process (CS90A)

Features

Technology Code |

|

| CS90A |

|

|

| |

Transistor | UHS | HS | ST | LL |

| ||

Physical Gate Length (nm) | 110 | 110 | 110 | 110 |

|

| |

Gate Oxide Thickness (nm) | 2.9 | 2.9 | 2.9 | 2.9 |

|

| |

Supply Voltage (V) | 1.2 | 1.2 | 1.2 | 1.2 |

|

| |

NMOS Ids (µA/µm) | 780 | 678 | 570 | 390 |

|

| |

PMOS Ids (µA/µm) |

|

| |||||

NMOS Ioff (nA/µm) | 36 | 4 | 0.18 | 0.005 |

|

| |

PMOS Ioff (nA/µm) |

|

| |||||

Mie plant | |||||||

Gate Leak Current (nA/µm) | 0.01 | 0.01 | 0.01 | 0.01 |

| ||

|

| ||||||

Basic Gate Delay (ps) | 14 | 17 | 28 | 45 |

|

| |

Number of Available Poly Layer |

|

| 1 |

|

|

| |

Number of Available Metal Layer |

|

| 8Cu+1Al |

|

|

| |

Via Filling |

| Cu Dual Damascene |

|

|

| ||

ILD Structure |

|

| Hybrid |

|

|

| |

SRAM Cell Size (µm2) |

|

| 1.98 |

|

|

| |

Dual Gate Oxide Options |

|

| Available |

|

|

| |

Mixed Signal Options |

|

| Available |

|

|

| |

RF Elements |

| MIM cap., Poly Resistor, Inductor |

|

|

| ||

Fuse |

| RAM Redundancy |

|

|

| ||

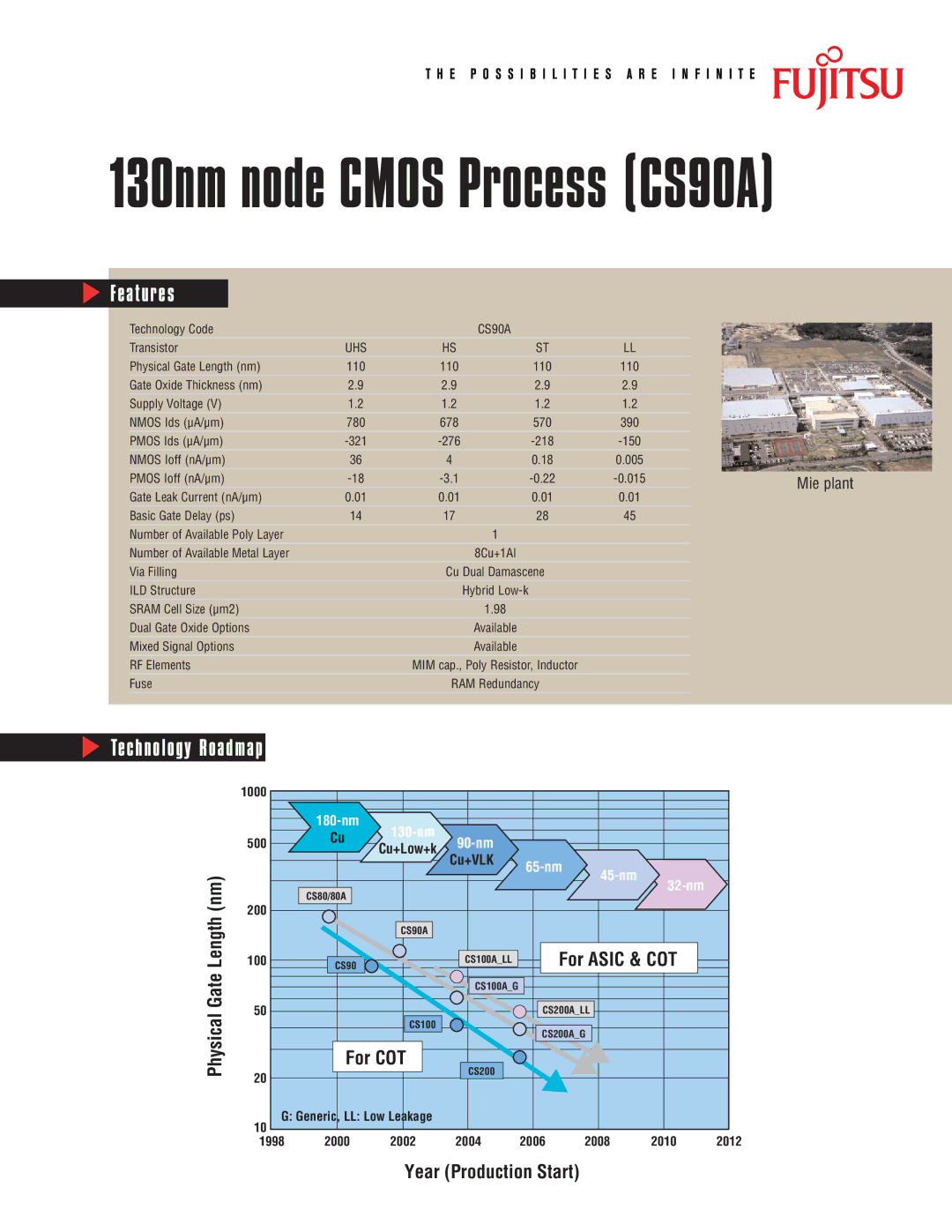

Technology Roadmap

| 1000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| 500 | Cu |

|

|

|

|

| ||

| Cu+Low+k |

|

|

|

|

| |||

|

|

|

|

|

|

| |||

|

|

| Cu+VLK |

|

|

|

|

| |

|

|

|

|

|

| ||||

(nm) |

|

|

|

|

|

| |||

|

|

|

|

|

|

| |||

| CS80/80A |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| ||

200 |

|

|

|

|

|

|

|

| |

Length |

|

|

|

|

|

|

|

| |

|

| CS90A |

|

|

|

|

|

| |

100 | CS90 |

| CS100A_LL |

| For ASIC & COT |

| |||

|

|

|

| ||||||

Gate |

|

|

| CS100A_G |

|

|

|

|

|

50 |

|

|

| CS200A_LL |

|

|

| ||

Physical |

| CS100 |

|

|

|

| |||

|

|

| CS200A_G |

|

|

| |||

|

|

|

|

|

|

| |||

20 | For COT | CS200 |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |

| G: Generic, LL: Low Leakage |

|

|

|

|

|

| ||

| 10 |

|

|

|

|

|

|

|

|

| 1998 | 2000 | 2002 | 2004 | 2006 | 2008 | 2010 | 2012 | |

Year (Production Start)