Page

Page

Hitachi Data Systems

Table of Contents

Hitachi Data Systems

Read-aheadfor High-performanceSequential Reads

Remote Copy

Hitachi NanoCopy Implementation Service

Hitachi Data Systems

Table of Figures

Tables

Hitachi Data Systems

Lightning 9900 Series Product Offerings

Introduction

The most advanced design in storage

The most powerful storage system in the world

Hitachi Data Systems

Introduction

Hitachi Data Systems

Mirrored cache instead of single image cache.1

Introduction

Hitachi Data Systems

Model 9960 Packaging

The Lightning 9900 Series

Packaging

Model 9960 Control Frame

Hitachi Data Systems

Model 9960 Array Frames

The Lightning 9900 Series Packaging

Model 9910 Packaging

Hitachi Data Systems

Figure 7 – A 9910 single-cabinetstorage subsystem

Series

Front-endDesign of the

Hitachi Lightning

Hitachi Data Systems

About the Fibre Channel Interface Boards

Page

Number of Host Interfaces Supported

Hitachi Data Systems

Bandwidth of Supported Host Interfaces

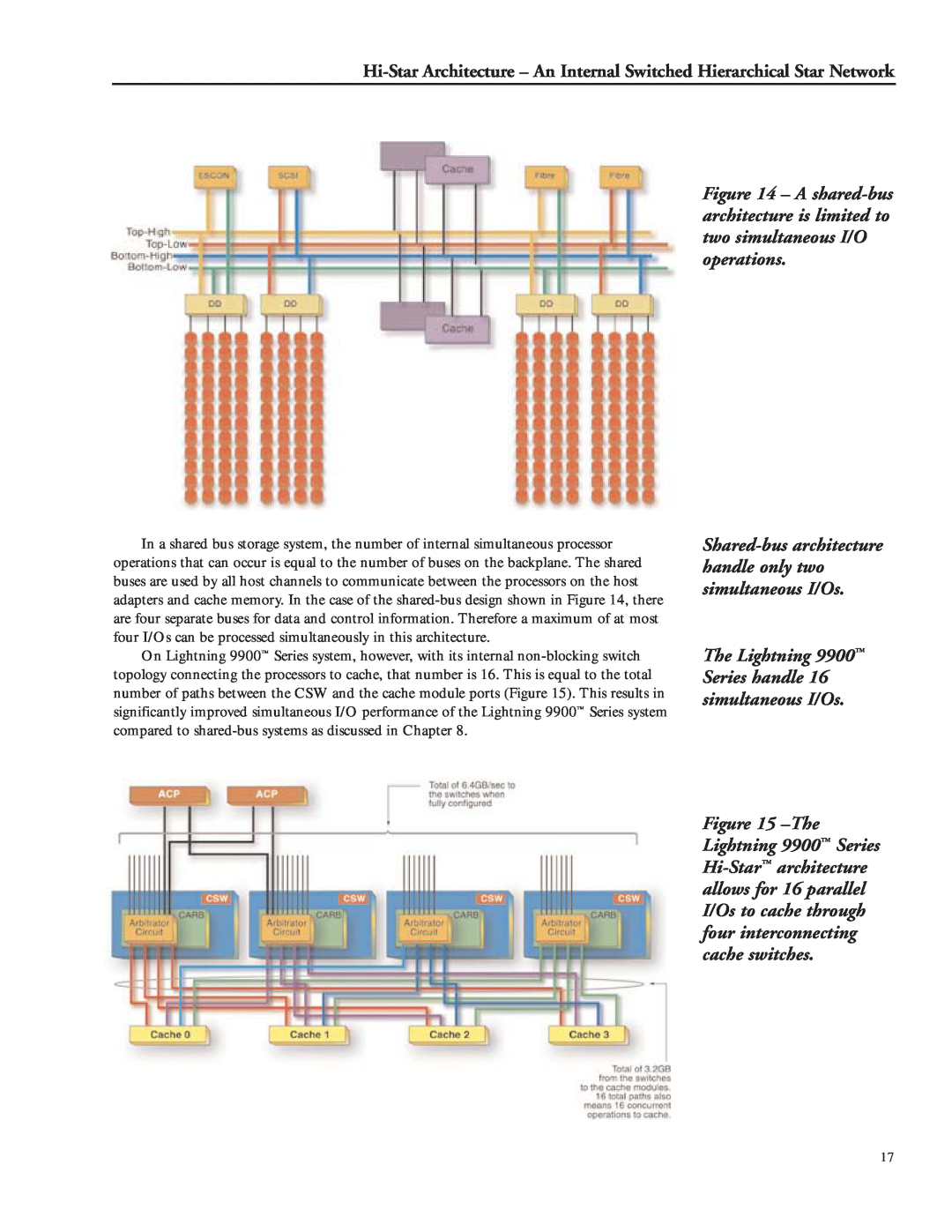

Hierarchical Star Network

Internal Switched

Hi-StarArchitecture – An

The Internal Hi-StarArchitecture

Hitachi Data Systems

Architecture

Page

Read-aheadfor High-performanceSequential Reads

Hitachi Data Systems

The 9960 Provides 32GB of Fully Addressable Cache

Control Memory Hierarchical Star Network

Page

Hitachi Data Systems

New Fibre Channel Disk Drives

High Performance Back-endDesign

High-speed Back-endDesign

The Importance of Command Tag Queuing CTQ

Command Tag Queuing greatly improves performance

Maximum Configuration of ACPs and Disks

Hitachi Data Systems

RAID-1+

Capacities and RAID Architecture

Storage Capacity of the Lightning 9900 Series

RAID-5- Distributed Parity

Hitachi Data Systems

High-densityDisk Drive Assemblies HDDs

Application Service Levels

Hitachi High-Availability Software Improves

Hitachi Data Systems

Open Systems High-AvailabilityMiddleware Support

3.Host Failover

4.Parallel Database Clustering

Standard Hot-swapand Redundant Power Supplies

Hitachi Data Systems

Standard Redundant Fans for Cooling

Unmatched Competitive Advantage in RAID Choices

Hitachi Data Systems

Performance Considerations

Truly Scalable Performance

Hitachi Data Systems

Test Results

Software Solutions for the

Software Solutions Are the

Best in the World

The Lightning 9900 Series

Figure 24 – Hitachi Data Systems offers a broad range of remote copy, data duplication, and data migration software solutions

Hitachi Data Systems

Data Migration

Remote Copy

PiT Copy

and warehousing

Hitachi Data Systems

Software Simplifies IT Operations

Centralized and Open

Systems Management

A powerful and open systems management philosophy

HiCommand is an important Hitachi management tool in that it provides a comprehensive storage management software framework that enables an enterprise to manage all supported Hitachi storage products and many Hitachi software solutions

Hitachi Data Systems

The components of HiCommand

Hitachi Resource Manager

Service Level Management

Hitachi Data Systems

Deployment Management

Hitachi LUN Manager is an open systems management utility. With Hitachi LUN Manager, open systems Logical Units LUNs can be defined, configured, and maintained. There is no more waiting for the hardware vendor to come and make configuration changes. Hitachi LUN Manager includes an easy-to-use, GUI-basedinterface that allows the easy definition of paths for LUNs, the reconfiguration of LUN-to-portassignments, or the viewing of the Lightning 9900 remote service information messages. Because the Hitachi LUN Manager can assign multiple paths to a single LUN, support of alternate path failover, path load balancing, and clustered systems is possible. Running on a standard Windows-basedPC connected to the storage subsystems by a dedicated LAN, Hitachi LUN Manager can support up to eight Lightning 9900 systems

Hitachi Data Systems

Hitachi CruiseControl

Storage Maximizer

Hitachi SANtinel

Hitachi Data Systems

Data Protection Services

Professional Services and Support

Professional Services Overview

Cost of Risk Analysis methodology CORA

Hitachi NanoCopy Implementation Service

Data Protection Services Lab

Remote Copy Assessment and Implementation Service

Hitachi Data Systems

On-lineData Migration Service

Professional Services and Support

Continuous Availability Service

SAN services

Software Portfolio Review and Analysis Service

Hitachi Data Systems

System Configurations for

the Performance Experiment

Hitachi Data Systems

The 7700E used all 6GB drives

100BaseT

Glossary of Terms

10BaseT

ACP pair

Back end

Hitachi Data Systems

Availability

Business Continuity Planning BCP

Cache

Glossary

CARB

CHIP

Control Frame

Hitachi Data Systems

Consistency Groups

CORA Cost of Risk Analysis

Data Duplication

Disaster Recovery

Glossary

Data Migration

Electronic vaulting

Hitachi Data Systems

EBCDIC

ESA/390

Fast Ethernet

Glossary

Failover

Fast write

FICON

File Backup

Hitachi Data Systems

Front End

HDmS

Hitachi FlashAccess

Glossary

Hitachi CruiseControl

Hitachi InstantSplit

Hitachi Multiplatform Backup/Restore

Hitachi Data Systems

Hitachi LUN Manager

Hitachi Resource Manager

Hitachi Rapid Recovery

Glossary

Hitachi SANtinel

HYPERtape

Hitachi Data Systems

HXRC Hitachi Extended Remote Copy

Java

Lightning 9900 Series

Logical Volume

Glossary

Logical Unit

MIPS

Hitachi Data Systems

MBCP

Meta-data

MTTR

Glossary

MTBF

NanoCopy

Open system

Hitachi Data Systems

On-linesystem

Operating System

RAID

Recovery Time

Glossary

RAID Controllers

SCSI

Switch

Hitachi Data Systems

Snapshot

Glossary

Virtual Logical Volume Image Manager

Volume

Synchronous

Workload

Hitachi Data Systems

Warm site

Asia Headquarters

Hitachi Data Systems Worldwide Offices

Corporate Headquarters

Australia/New Zealand Headquarters