When the driving current is increased, input voltage of the differential amplifier (pin 2) will be increased. In such cases, the differential amplifier output voltage (pin 1) is decreased to reduce the driving current.

4-3 PLL CIRCUIT

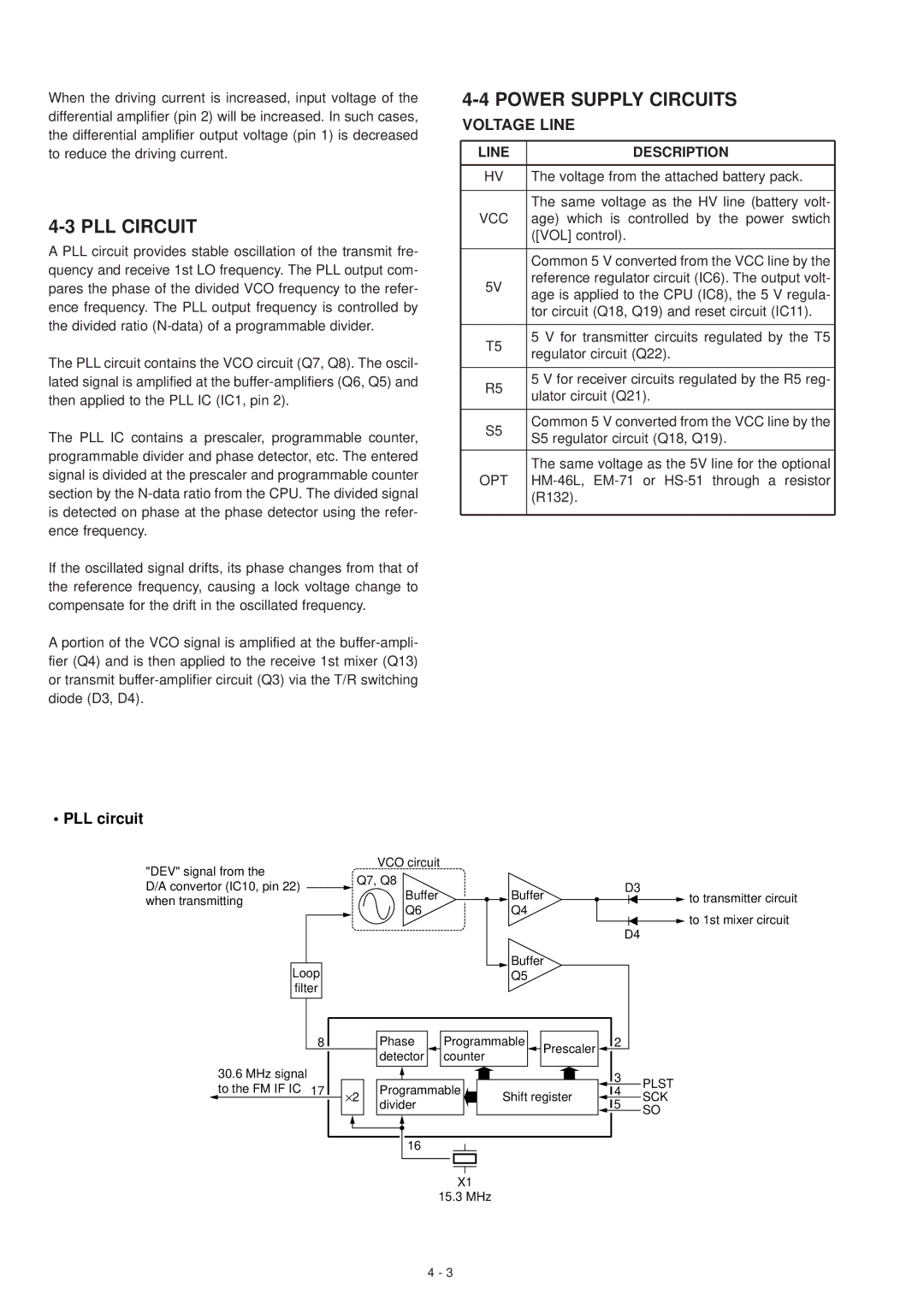

A PLL circuit provides stable oscillation of the transmit fre- quency and receive 1st LO frequency. The PLL output com- pares the phase of the divided VCO frequency to the refer- ence frequency. The PLL output frequency is controlled by the divided ratio

The PLL circuit contains the VCO circuit (Q7, Q8). The oscil- lated signal is amplified at the

The PLL IC contains a prescaler, programmable counter, programmable divider and phase detector, etc. The entered signal is divided at the prescaler and programmable counter section by the

If the oscillated signal drifts, its phase changes from that of the reference frequency, causing a lock voltage change to compensate for the drift in the oscillated frequency.

A portion of the VCO signal is amplified at the

4-4 POWER SUPPLY CIRCUITS VOLTAGE LINE

LINE | DESCRIPTION | |

|

| |

HV | The voltage from the attached battery pack. | |

|

| |

| The same voltage as the HV line (battery volt- | |

VCC | age) which is controlled by the power swtich | |

| ([VOL] control). | |

|

| |

| Common 5 V converted from the VCC line by the | |

5V | reference regulator circuit (IC6). The output volt- | |

age is applied to the CPU (IC8), the 5 V regula- | ||

| ||

| tor circuit (Q18, Q19) and reset circuit (IC11). | |

|

| |

T5 | 5 V for transmitter circuits regulated by the T5 | |

regulator circuit (Q22). | ||

| ||

|

| |

R5 | 5 V for receiver circuits regulated by the R5 reg- | |

ulator circuit (Q21). | ||

| ||

|

| |

S5 | Common 5 V converted from the VCC line by the | |

S5 regulator circuit (Q18, Q19). | ||

| ||

|

| |

| The same voltage as the 5V line for the optional | |

OPT | ||

| (R132). | |

|

|

• PLL circuit

"DEV" signal from the

D/A convertor (IC10, pin 22) when transmitting

Loop

filter

VCO circuit

Q7, Q8

Buffer Q6

![]() Buffer

Buffer

Q4

Buffer

Q5

D3

![]() to transmitter circuit

to transmitter circuit

![]() to 1st mixer circuit D4

to 1st mixer circuit D4

30.6MHz signal to the FM IF IC

8 |

| Phase | Programmable | Prescaler | 2 |

| ||

|

| detector | counter |

|

|

| ||

|

|

|

|

|

| |||

17 |

| Programmable |

|

| 3 | PLST | ||

⋅2 | Shift register | 4 | ||||||

SCK | ||||||||

| divider |

| 5 | |||||

|

|

|

|

| SO | |||

|

|

|

|

|

|

| ||

|

| 16 |

|

|

|

|

| |

X1

15.3 MHz

4 - 3