MCS4 | MCS4 KIT A |

Microcomputer Kit

MCS~4 - INTEL'SLOWEST COST MICROCOMPUTER.

IDEAL FOR PROTOTYPE OR LOW VOLUME PRODUCTION.

• Programmable General |

Purpose Microcomputer |

• |

Instructions |

The

The 4008 and 4009 are a pair of inter- face devices which expand the capa- bilities of

Asystem built with the

requiring any interface logic. By adding a few simple gates the

The

The Intel

• | Instruction Set includes |

| Conditional Branching, |

| Jump to Subroutine and |

| Indirect Fetching |

• | Binary and Decimal |

| Arithmetic Modes |

• Program Storage in 4702A | |

| Reprogrammable PROM |

| Simulates 4001 ROM |

• | |

• | 10.8 Microsecond |

| Instruction Cycle |

• | CPU Directly Compatible |

| with |

| RAMs Using 4008/4009 |

| Standard Memory ana |

| 1/0 Interface Set |

• Easy | |

| can Directly Drive up to |

| 32,768 Bits of ROM and up |

| to 5120 Bits of RAM |

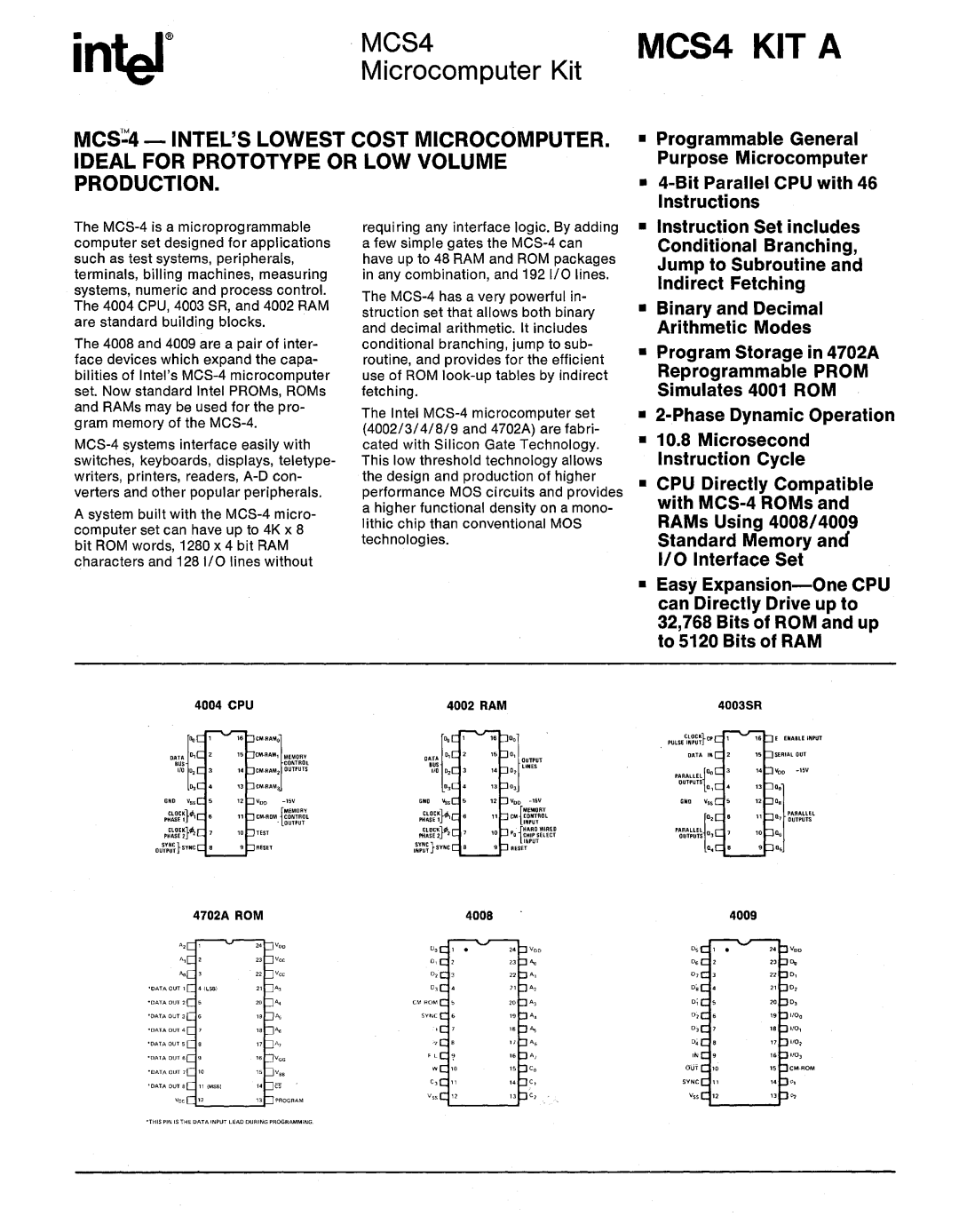

| 4004 CPU |

|

|

|

| 4002 RAM |

|

|

|

|

| 4003SR | |||||||

~"f0, |

|

|

|

|

|

|

|

|

|

|

|

|

| PULSE ~~~~*p |

|

| |||

I | 16 |

|

|

|

|

|

| I | 16 |

|

|

|

| I | |||||

|

|

| CM·RAM3 | MEMORY | 03 |

|

|

| 0 3 |

|

|

| n, |

| 13 | ||||

|

|

|

|

| CM·RAM, |

|

|

|

|

|

| 0, |

| OUTPUTS |

|

|

|

| |

|

|

|

|

| ""l |

|

|

|

|

|

| 'j |

|

|

|

| |||

BUS |

|

|

|

|

|

| CONTROL |

| BUS |

|

|

|

| OUTPUT |

|

|

|

|

|

GNO | Vss | 5 | 12 |

| Voo |

| ""f |

| 12 |

| Voo |

|

|

|

|

| |||

I/O | 0, |

|

|

| CM.RAM, |

| OUTPUTS | 1100, |

|

|

| O | LINES |

|

|

|

| 3 | |

|

|

|

|

|

|

| 2 |

| PARALLEL{Oo |

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

p~~g~~}<p, | 6 | II |

| CM·ROM |

| CONTROL |

| p~~i~}<p, | 6 | II |

| CM | CONTROL |

| f |

| 6 | ||

|

|

|

|

|

| {MEMORY |

|

|

|

|

| {MEMORY |

|

|

| ||||

p~~~m<p, | 7 |

|

| . |

| OUTPUT | p~l~g}<P, | 7 | 10 |

| Po | INPUT |

|

|

| ||||

|

|

|

|

|

| CHIPSELECT | OUTPUTS | 3 |

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ·lHAROWIREO | PARALLEL |

| 0 |

|

| |

Ou;~~nSYNC |

|

|

|

|

|

| I~~~~}SYNC | 8 | 9 |

|

| INPUT |

|

|

|

|

| ||

8 |

|

|

|

|

|

| RESET |

|

| O. |

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

')a.

a PARALLEL 7 OUTPUTS

a.

05

4702A ROM | 4008 | 4009 |

·THISPIN IS THE DATA INPUT LEAD DURING PROGRAMMING.