LED TV

MODEL 32LA62** 32LA62**-Z

SERVICE MANUAL

READ THE SAFETY PRECAUTIONS IN THIS MANUAL

SERVICING PRECAUTIONS

CONTENTS

CONTENTS

SAFETY PRECAUTIONS

IMPORTANT SAFETY NOTICE

SAFETY PRECAUTIONS

Electrostatically Sensitive ES Devices

SERVICING PRECAUTIONS

Removal

IC Remove/Replacement

Replacement

Small-Signal Discrete Transistor Removal/Replacement

3. Test method

SPECIFICATION

4. Model General Specification

1. Application range

DVB-S QPSK 2 ~ 45Msymbol/s

Symbolrate 4.0Msymbols/s to 7.2Msymbols/s

symbolrate

DVB-S2 8PSK / QPSK 2 ~ 45Msymbol/s

5. Component Video Input Y, Pb, Pr

6.2. PC mode

6. HDMI Input 6.1. DTV mode

7.1. HDMI 1.4b 3D supported mode automatically

7.5. USB Input 3D supported mode manually

7.2. HDMI Input1.3

7.3. RF Input3D supported mode manually

7.4. RF Input 3D supported mode automatically

7.9. 3D Input mode

7.6. HDMI-PC Input 3D supported mode manually

7.7. DLNA Input 3D supported mode manually

7.8. Component Input3D 3D supported mode manually

2. Designation

ADJUSTMENT INSTRUCTION

3. Automatic Adjustment

1. Application Range

3.5. CI+ Key checking method

3.3. LAN PORT INSPECTIONPING TEST

SET PC

3.4. Model name & Serial number Download

3.6. WIFI MAC ADDRESS CHECK

4. Manual Adjustment

4.1. EDID DATA

4.2.1. Overview

4.2. White Balance Adjustment

4.2.4. Adj. Command Protocol

4.1.2. 2D EDID

4.2.6. Reference White balance Adj. coordinate and color temperature

4.2.5. Adj. method

4.2.7. ALELF & EDGE LED White balance table

4.5. 3D function test

4.4. Magic Motion Remote control test

4.6. Wi-Fi Test

4.3. Local Dimming Function Check

8. Audio

7. GND and Internal Pressure check

5. Tool Option selection

6. Ship-out mode checkIn-stop

After downloading, have to adjust Tool Option again

9. USB S/W DownloadService only

reserved

DIAGRAM

BLOCK

LGE2122

EXPLODED VIEW

Model Option

EAX64797001* LD33B EAX64872101* LA33B

NVRAM

X-TAL

IC105 LGE2122A2M13

PLACE AT JACK SIDE

IC105

LGE2122A2M13

ZD500

PLACE AT MAIN SOC SIDE

PLACE AT JACK SIDE

PLACE AT IC6000

IC703 K4B4G1646B-HCK0

DDR512MBSS

IC701

K4B4G1646B-HCK0

Copyright 2013 LG Electronics. Inc. All rights reserved

+5VNormal

PANELPOWER

PowerDET

FROM LPB & PSU

GP4 High/MID Power SEQUENCE

Renesas MICOM

For Debug

MICOM MODEL OPTION

HDMI3

SIDE

2011.11.21

SPDIF

SPDIF OUT

JACK HIGH / MID

JACKCOMMON

UART FOR DEBUG

AV/COMPONENT REAR

1/16W

MAX 0.4A

MREMOTE&WIFIWAFER

AR4100

IC4306

OCP USB2/3

USB2 MAX 1.5A

USB3 MAX 1.5A

IC4500

USB1

OCP USB1

MAX 1.5A

2011.10.26

Full Scart18 Pin Gender

JK4600

SCART GENDER

LANVERTICAL

Ethernet Block

2012.03.08

AMPMUTEPWRDET

0x54

IC6000

SCART AUDIO MUTE

AZ4580MTR-E1

HEADPHONE AMP

EARPHONE AMP 18pF

2011.09.29

CI SLOT

CI POWER ENABLE CONTROL

2011.10.31

+5VNORMAL

B-CAS SMART CARD INTERFACE

+3.3VNORMAL

TDA8024TT

Vout=0.6*1+R1/R2

TDSS-G501DB

TU6600

TU6601

TU6602

JP6800

RS-232C Control INTERFACE

JP6801

Ouput trace widths should be sized to conduct at least 2A

DVB-S2 LNB Part Allegro

OptionLNB

Input trace widths should be sized to conduct at least 3A

LVDSHIGHMID

LVDS

51Pin LVDS OUTPUT Connector

41Pin LVDS OUTPUT Connector

I2CSCL1 L/DIMOUT8P R7602

LOCAL DIMMING

P7600 12507WR-08L L/DIMOUT8P

R7601 10K L/DIMOUT8P L/DIM0SCLKPWR L/DIM0MOSIPWR R7603

T-Con

POWER BLOCK

THIS IS REVERSE PATTERN

LEVEL SHIFTER BLOCK

LGE Internal Use Only

EMMC

Don’t Connect Power At VDDI

eMMC I/F

Just Interal LDO Capacitor

+24VAMP OPT C5450 10uF 35V

DEMODTSVAL ExtTsVAL DEMODTSDATA1 EXT2TsCLK DEMODTSDATA3 EXT2TSSync

JAPAN TUNER INTERFACE

USE Two serial TS Port for Japan MTK A2 Ball Name Function

DEMODTSCLK ExtTSCLK DEMODTSSYNC ExtTSSync DEMODTSDATA0 ExtTsD0

Page

XXLA64/62/61*-Z XXLN57*-Z

Applicable Model Mid-end Platform XXLA74*-Z XXLA71*-Z XXLA69/66*-Z

2013 LED/LCD TV Engineering guide

4. Structure of TV set and connection of sub ass’ys 5. New sub ass’ys

CONTENT

1. New features 2. Main PCBs 3. Block Diagrams, IIC Map

Instruction of new sub ass’ys 6. Adjust way of new features

EPI Interface

EPIEmbedded Point-Point Interface Features

Merits

Comparison

EPI Interface mini-LVDS vs. EPI

HF mini-LVDS TCON

EPI TCON

Protocol

Features

HF mini-LVDS

Topology

From TV to Smart phone

NFC Near field communication

User Action Area

NFC Tag

Chassis LD33B

Main PCB for Broadband

WIFI/BT

xxLA660S-Zx

1. LGE2122 Block Diagram

2. LGE 2122 I2C Block Diagram

IC105 LGE

3.5V

3. Power Block Diagram

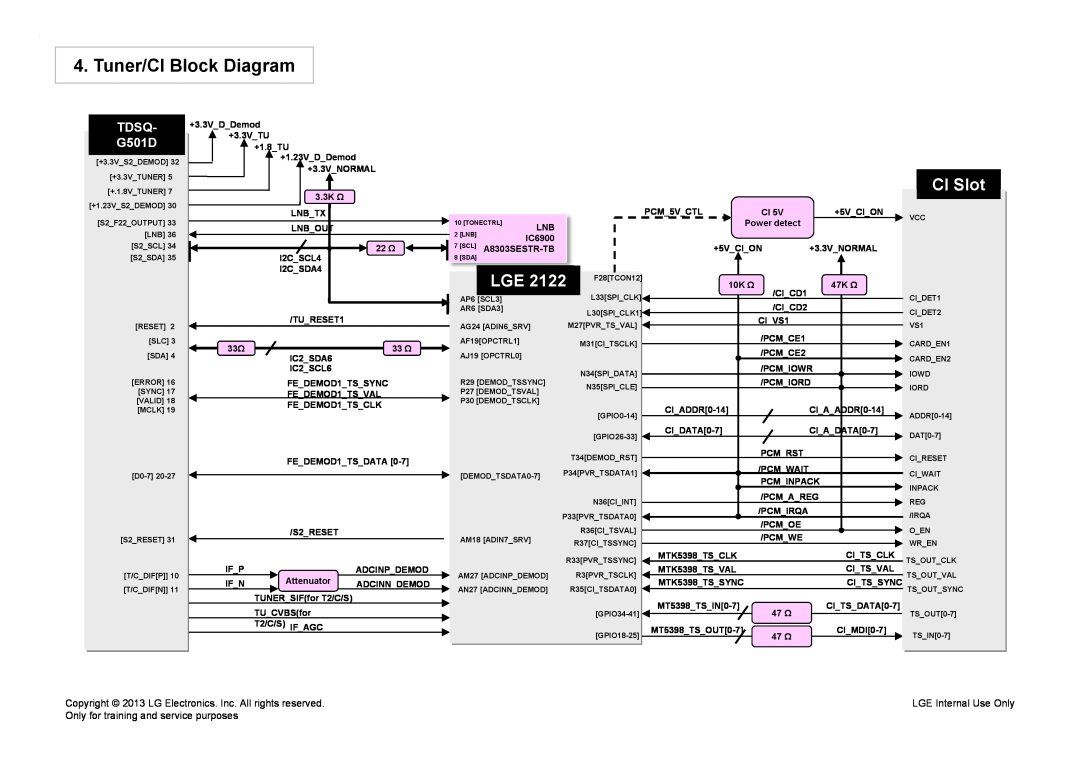

TDSQ G501D

CI Slot

Jack Side

5. Video/Audio In Block Diagram

SoC Side

Tuner

6. Audio Out Block Diagram

RENESAS WOLCTL MICOM

HDMI1

HDMI2

HDMI3

TPS65198

PMIC

Level Shift

TPS65178

9. PMIC & Level Shift Bloc Diagram

USBDM1 USBDP1 /USBOCD1 USBCTL1

Motion Remote Receiver

4Pin debugging wafer

RENESAS MICOM

47LA660S-ZA

Interconnection

PCBs

Cables

7 IR to Local Key 3Pin Cable 8 IR to Logo Assy 4Pin Cable

6 IR Assy

1. System 2. Remote Buttons 3. MR13 Block Diagram 4. Function List

Introductions of 13Y RF ass’y + Magic Remote control

5. Pairing/Un-pairing Method

Motion Data Transmission

1. System

Pairing Information Transmission Send to TV after Paired

Pairing Information Transmission Sequence

repeat

2. Remote Buttons M4 vs. MR13

M4 Remote

MR13 Remote

Bluetooth Receiver

3. MR13 Block Diagram

Power Management

Bluetooth Remote control

RF, Gyro, Accelerometer Power Supply

4. Function list

Wireless communication

Battery Boost up Regulator

Method

5. RF Pairing / Un-pairing Method

Description

1. Wi-Fi built in Ass’y feature 2. Wi-Fi built in Ass’y specification

Introductions of 13Y WIFI built in ass’y

Wafer

WIFI Built in ass’y feature

Pin map

Switch

WIFI Built in ass’y Specification

2012. 12

Widevine & HDCP 2.0 & NETFLX

1. Widevine? 2. HDCP 2.0 & NETFLIX? 3. DTCP? 4. Changed BOM

Contents

1. Widevine?

HDCP

2. HDCP 2.0 & NETFLIX?

Netflix

Why HDCP2.0?

3. DTCP?

Changed Item

4. Changed BOM

As-Was

Current

Contents of LCD TV Standard Repair Process

Page

Contents of LCD TV Standard Repair Process Detail Technical Manual

Error symptom

Content

Replace T-con Board or module And Adjust VCOM

Main B/D↔ Power B/D, LVDS Cable,Speaker Cable,IR B/D Cable

Check Power Board 24v output

Check Power Board 12v,3.5v etc

3.5V,12V,20V or 24V…

Check various voltages of Power Board

Check RF Signal level

By using Digital signal level meter By using Diagnostics menu on OSD

Menu→ Set up→ Support → Signal Test

Signal strength Normal over 50% Signal Quality Normal over 50%

→ Set-Top-Box, Different maker TV etc

A. Picture Problem DVB-S/S2

replace Link

A10/ A11

Check color by input -External Input COMPONENT

※ Check and

A10/ A11

External device screen error-Color error

Vertical/Horizontal bar, residual image, light spot

Replace Main B/D adjust VCOM

Check ST-BY

Check Power LED

Check Power On ‘”High”

Measure voltage of each output of Power B/D

POWEROFFCPUABNORMAL

Check Power Off Mode

If Power Off mode is not displayed Check Power B/D voltage

POWEROFFABNORMAL1

Check user menu Speaker off

Check audio B+ 24V of Power Board

Check audio B+ Voltage

In case of External Input signal error Check and fix external device

Power B/D don’t have problem

Check & Repair Cable connection Connector solder

Check IR Output signal

Check 3.5v on Power B/D Replace Power B/D or Replace Main B/D

External device recognition error

D. Function error

Identify noise type

F. Exterior defect

Adjust VCOM

G. Network Error

Check SVC Bulletin

Check defect CI slot pin

Continued from previous page

ALL MODELS

Standard Repair Process Detail Technical Manual

Entry method

Check the DC 24V, 12V

24 Pin Power Board ↔ Main Board

SMAW200-H24S

MENU support signal test select channel

A. Video errorVideo error, video lag/stop

When the signal is strong, use the attenuator -10dB, -15dB, -20dB etc

ALL MODELS

1. Checking method for remote controller for adjustment

Press the IN-START with the remote controller for adjustment

Version

image, light spot

A. Video error Vertical/Horizontal bar, residual

Checking method

4.Video error Classification of MODULE or Main-B/D

A. Video errorColor error

You can view 6 types of patterns using the ADJ Key

MODULE error ADD-BAR,SCAN BAR

Solder defect, Short/Crack

Appendix Exchange EPI Cable or Main B/D

Abnormal Power Section

Solder defect, CNT Broken

Noise

Fuse Open, Abnormal power section

Abnormal Display

GRADATION

No Light

Appendix Exchange LPBLED driver

Dim Light

Panel Mura, Light leakage

Appendix Exchange the Module

Un-repairable Cases In this case please exchange the module

Panel Mura, Light leakage Crosstalk Press damage

Un-repairable Cases In this case please exchange the module

Front LOGO LED control in the status of ST-BY Condition

For ’10 models, there is no voltage out for st-by purpose

When st-by, only 3.5V is normally on

Checking method when power is ON

Check “power on” pin is high

Entry method

1. Press the IN-START button of the remote controller for adjustment

2. Check the entry into adjustment item

B. Power error Off when on, off whiling viewing

3. Change TV Sound Out to TV Speaker

C. Audio errorNo audio/Normal video

1. Press the MENU button on the remote controller

2. Select the SOUND function of the Menu

Checking order when there is no audio

③ ④ ② ①

LCD module change T-Con board change