Mercury can configure systems with hundreds of compute nodes, communicating over the

AltiVec Vector Processing Unit

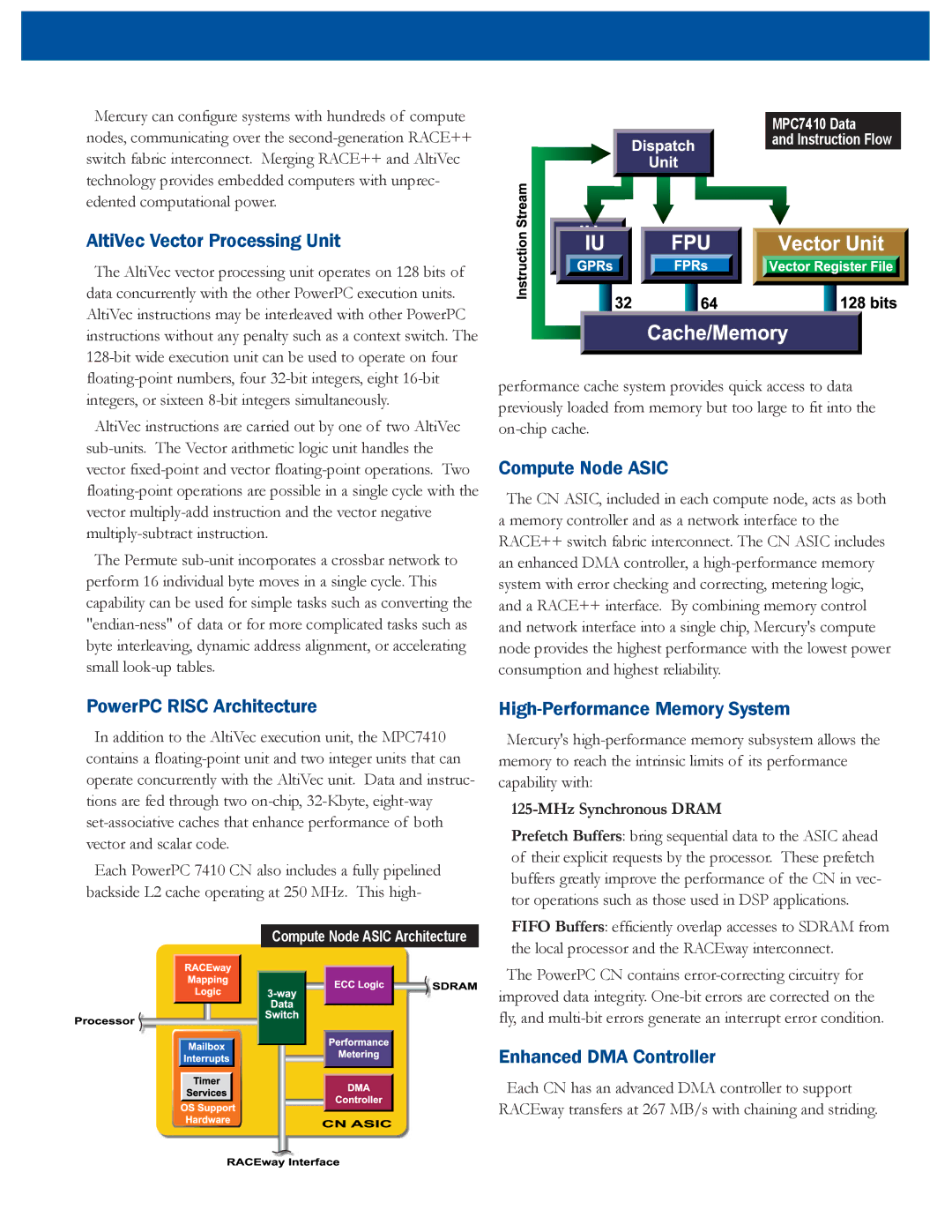

The AltiVec vector processing unit operates on 128 bits of data concurrently with the other PowerPC execution units. AltiVec instructions may be interleaved with other PowerPC instructions without any penalty such as a context switch. The

AltiVec instructions are carried out by one of two AltiVec

The Permute

MPC7410 Data

and Instruction Flow

performance cache system provides quick access to data previously loaded from memory but too large to fit into the

Compute Node ASIC

The CN ASIC, included in each compute node, acts as both a memory controller and as a network interface to the RACE++ switch fabric interconnect. The CN ASIC includes an enhanced DMA controller, a

PowerPC RISC Architecture

In addition to the AltiVec execution unit, the MPC7410 contains a

Each PowerPC 7410 CN also includes a fully pipelined backside L2 cache operating at 250 MHz. This high-

Compute Node ASIC Architecture

High-Performance Memory System

Mercury's

125-MHz Synchronous DRAM

Prefetch Buffers: bring sequential data to the ASIC ahead of their explicit requests by the processor. These prefetch buffers greatly improve the performance of the CN in vec- tor operations such as those used in DSP applications.

FIFO Buffers: efficiently overlap accesses to SDRAM from the local processor and the RACEway interconnect.

The PowerPC CN contains

Enhanced DMA Controller

Each CN has an advanced DMA controller to support RACEway transfers at 267 MB/s with chaining and striding.