500 MHz PowerPC

7410 Daughtercard

Embedded computing reaches a new level of performance with RACE++® Series

PowerPC® 7410 daugh- tercards from Mercury Computer Systems.

Each PowerPC 7410 daughtercard contains two

500 MHz MPC7410 microprocessors with AltiVec™ technology. These unique microprocessors combine a modern super- scalar RISC architecture with an AltiVec parallel vector execution unit.

To keep the processor fed with ample data, increased emphasis is placed on the memory system and communications fabric that delivers data to the processor. Each compute node on the 500 MHz PowerPC 7410 daughtercard has a dedicated fabric interface at 267 MB/s and maximum mem- ory speed of 125 MHz. By maximizing the performance of the memory and the fabric interface to the processor, Mercury has optimized RACE++ compute nodes for processing continuous streams of data.

AltiVec in RACE++ Computers

AltiVec Parallel Vector Technology

Scalable from Two to Hundreds of Processors

1K CFFT in 20 ∝s on Each Processor

125 MHz Memory System with Prefetch and ECC

Advanced DMA Engine for Chained Submatrix Moves

267 MB/s RACE++

Switch Fabric

Interconnect

Fast L2 Cache (250 MHz)

The AltiVec vector processing unit revolutionizes the performance of computationally intensive applications such as image and signal processing. Each vector unit can operate in parallel on up to four

AltiVec technology also represents a leap in simplifying the programming required to achieve high performance. Whereas previous

Optimized Performance

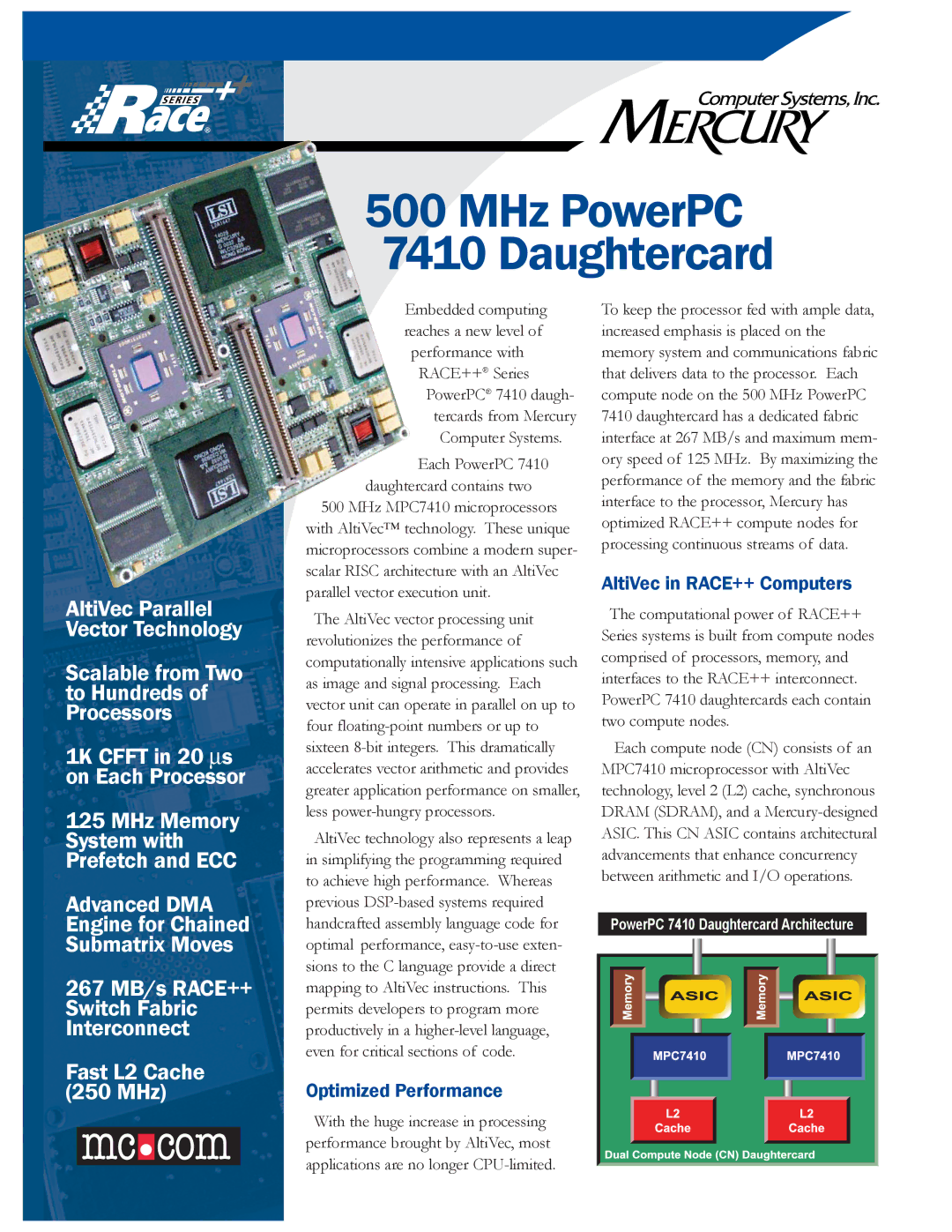

The computational power of RACE++ Series systems is built from compute nodes comprised of processors, memory, and interfaces to the RACE++ interconnect. PowerPC 7410 daughtercards each contain two compute nodes.

Each compute node (CN) consists of an MPC7410 microprocessor with AltiVec technology, level 2 (L2) cache, synchronous DRAM (SDRAM), and a

PowerPC 7410 Daughtercard Architecture

With the huge increase in processing performance brought by AltiVec, most applications are no longer