Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

DSP56362

|

|

|

| DSP56362 |

|

| L/R | Left/Right |

PCM or |

|

|

|

|

|

| I2S | |

Compresse |

|

|

|

|

|

| Tx | Stereo Out |

|

|

|

|

|

|

| ||

I2S |

|

|

| User | Buffer |

|

| |

d Data | Dolby |

| Dolby | C/Sub | Center/ | |||

Rx |

| |||||||

| Digital |

| Defined | Subwoofer | ||||

|

|

| Pro Logic | I2S | ||||

|

|

|

|

| Processing: | Output Delay | Tx | Out |

|

|

|

|

|

|

| ||

|

|

| Select | Select | — Bass mgt | Sr/Sl | Right/Left | |

| Input | MPEG2 | — 3D Virtual | |||||

| 2 | Surround | ||||||

| Buffer | 5.1/7.1 | Surround | I S | Sound Out | |||

| — Lucasfilm | Tx | ||||||

|

|

|

|

| ||||

|

|

| THX5.1 | L/R |

| |||

|

|

|

|

|

|

| ||

| Auto |

|

| Noise | — Soundfields |

| Headphone | |

| DTS |

| — Equalization |

| I2S | Mix Down/ | ||

| Detector |

| Sequencer |

|

| Tx | ||

|

|

|

| Aux. Sur- | ||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| round |

|

|

|

|

|

|

| IEC958 |

|

|

|

| DSP Clock |

|

| Tx |

| |

|

|

|

|

|

|

| ||

| Parallel | PLL | General | Serial | JTAG/OnCE™ |

| ||

| Host/Data | Purpose | Host |

| ||||

|

|

|

| Interface |

| |||

| Interface |

|

| I/O | Interface |

|

| |

|

|

|

|

|

| |||

External | System | User | SPI/I2C | Dedicated |

|

Host CPU/ | Clock | Programmable | Protocol | Debugging |

|

| I/O |

| Port | AA0565G |

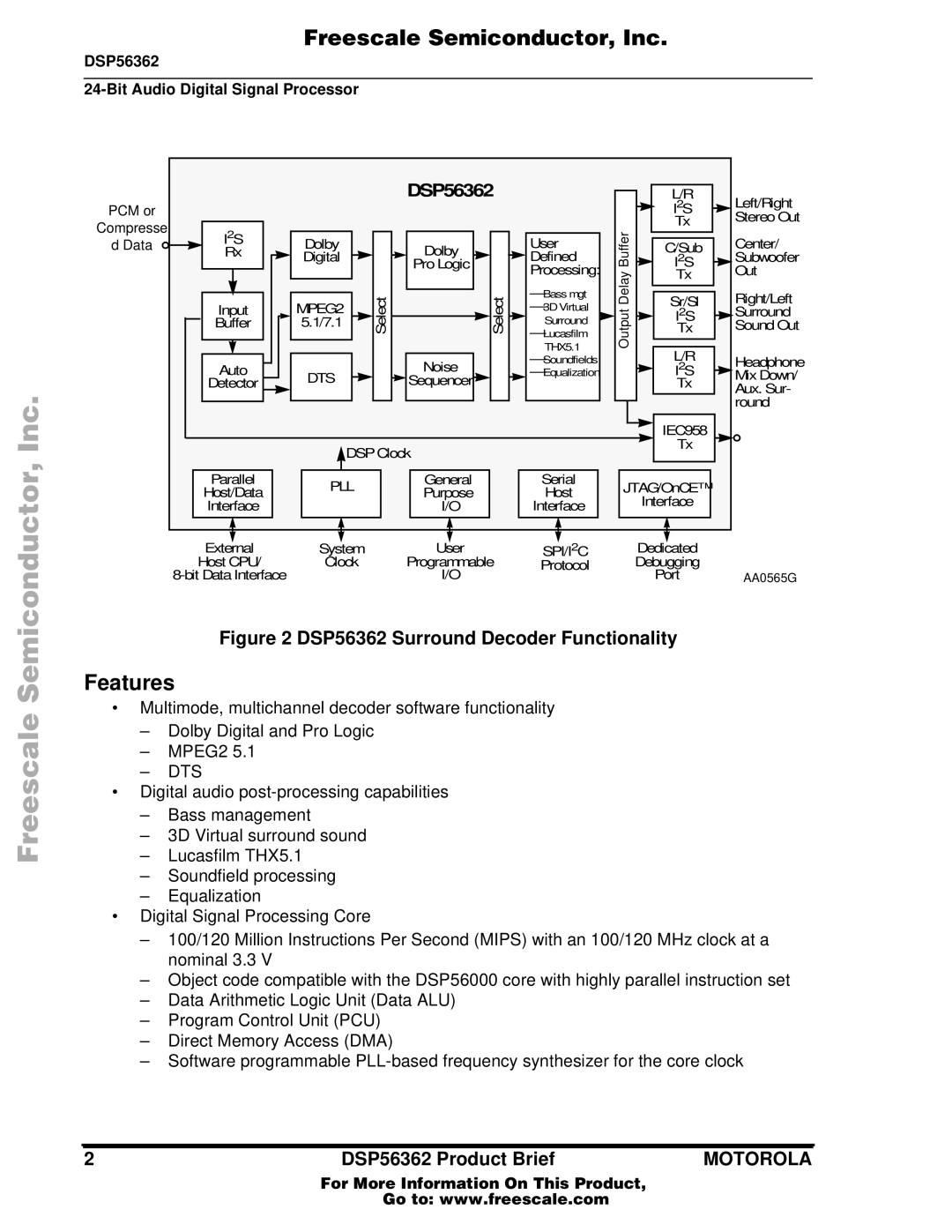

Figure 2 DSP56362 Surround Decoder Functionality

Features

•Multimode, multichannel decoder software functionality

–Dolby Digital and Pro Logic

–MPEG2 5.1

–DTS

•Digital audio

–Bass management

–3D Virtual surround sound

–Lucasfilm THX5.1

–Soundfield processing

–Equalization

•Digital Signal Processing Core

–100/120 Million Instructions Per Second (MIPS) with an 100/120 MHz clock at a nominal 3.3 V

–Object code compatible with the DSP56000 core with highly parallel instruction set

–Data Arithmetic Logic Unit (Data ALU)

–Program Control Unit (PCU)

–Direct Memory Access (DMA)

–Software programmable

2 | DSP56362 Product Brief | MOTOROLA |

For More Information On This Product,

Go to: www.freescale.com