Operating Precautions for VR4133 TM

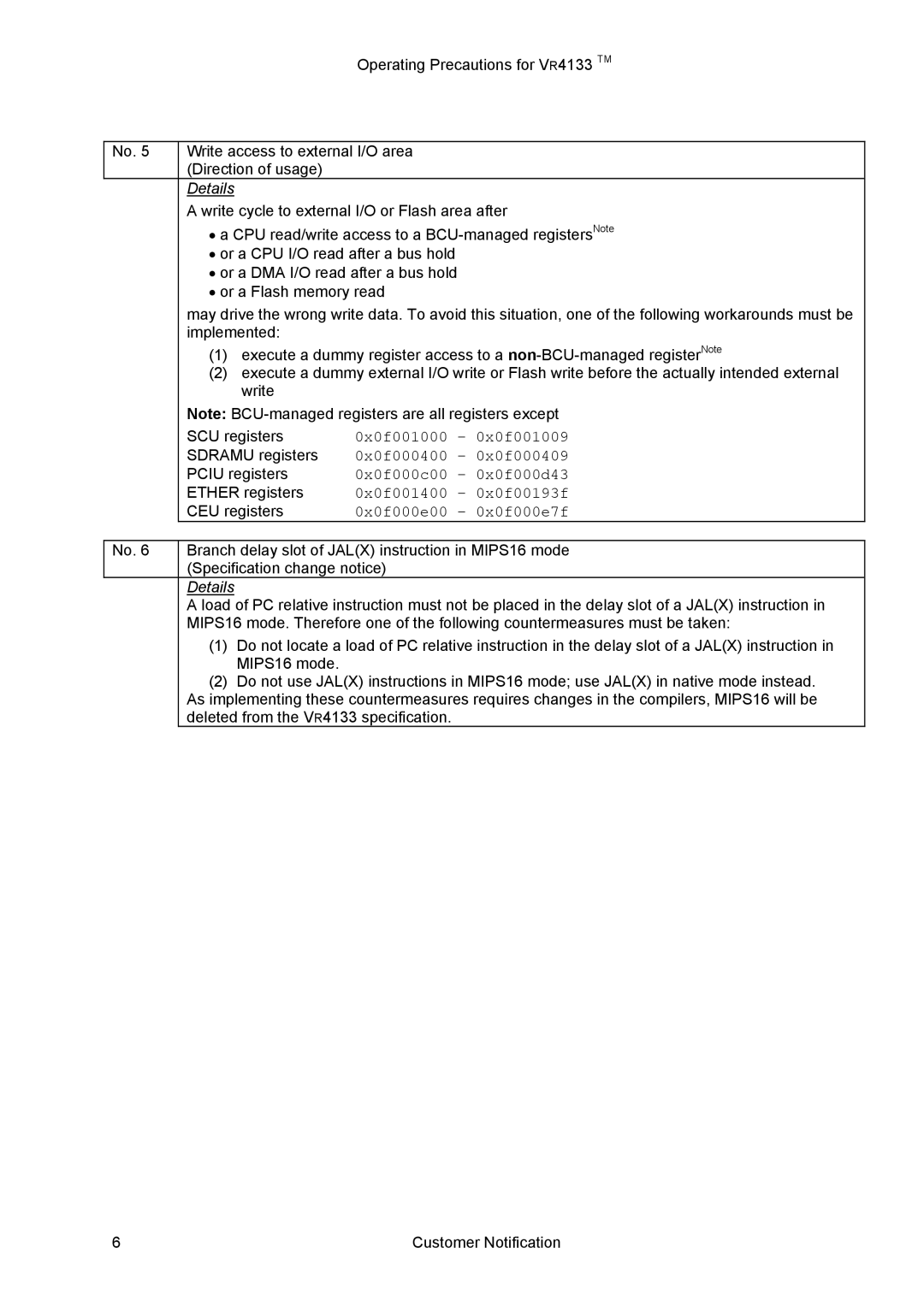

No. 5 | Write access to external I/O area |

| (Direction of usage) |

| Details |

| A write cycle to external I/O or Flash area after |

| • a CPU read/write access to a |

| • or a CPU I/O read after a bus hold |

| • or a DMA I/O read after a bus hold |

| • or a Flash memory read |

may drive the wrong write data. To avoid this situation, one of the following workarounds must be implemented:

(1)execute a dummy register access to a

(2)execute a dummy external I/O write or Flash write before the actually intended external write

Note:

| SCU registers | 0x0f001000 – 0x0f001009 | |

| SDRAMU registers | 0x0f000400 – 0x0f000409 | |

| PCIU registers | 0x0f000c00 – 0x0f000d43 | |

| ETHER registers | 0x0f001400 – 0x0f00193f | |

| CEU registers | 0x0f000e00 – 0x0f000e7f | |

|

| ||

No. 6 | Branch delay slot of JAL(X) instruction in MIPS16 mode | ||

| (Specification change notice) | ||

| Details |

|

|

| A load of PC relative instruction must not be placed in the delay slot of a JAL(X) instruction in | ||

| MIPS16 mode. Therefore one of the following countermeasures must be taken: | ||

| (1) | Do not locate a load of PC relative instruction in the delay slot of a JAL(X) instruction in | |

|

| MIPS16 mode. |

|

| (2) | Do not use JAL(X) instructions in MIPS16 mode; use JAL(X) in native mode instead. | |

| As implementing these countermeasures requires changes in the compilers, MIPS16 will be | ||

| deleted from the VR4133 specification. | ||

6 | Customer Notification |