Operating Precautions for VR4133 TM

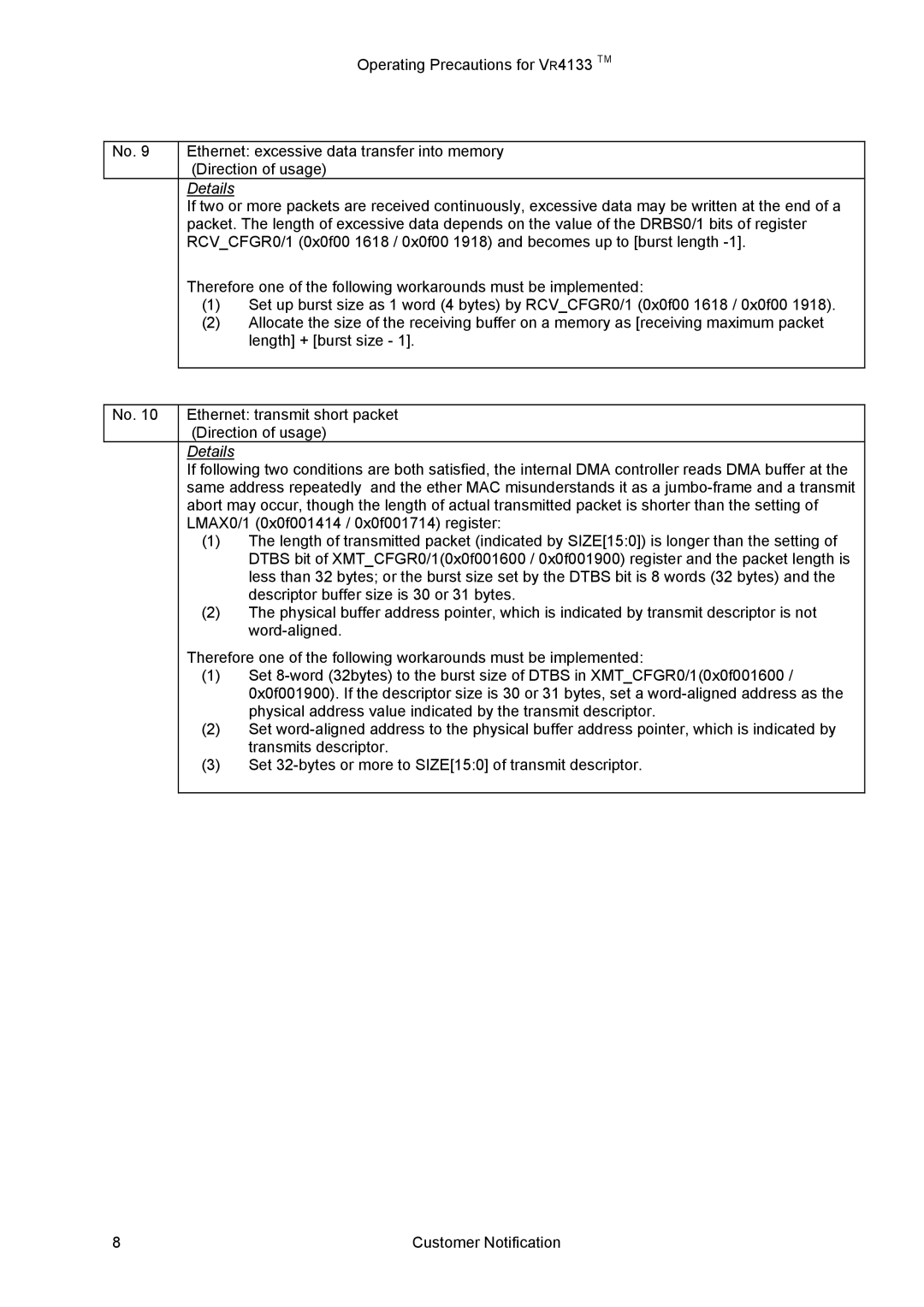

No. 9 | Ethernet: excessive data transfer into memory |

| (Direction of usage) |

| Details |

| If two or more packets are received continuously, excessive data may be written at the end of a |

| packet. The length of excessive data depends on the value of the DRBS0/1 bits of register |

| RCV_CFGR0/1 (0x0f00 1618 / 0x0f00 1918) and becomes up to [burst length |

Therefore one of the following workarounds must be implemented:

(1)Set up burst size as 1 word (4 bytes) by RCV_CFGR0/1 (0x0f00 1618 / 0x0f00 1918).

(2)Allocate the size of the receiving buffer on a memory as [receiving maximum packet length] + [burst size - 1].

No. 10 | Ethernet: transmit short packet |

| (Direction of usage) |

| Details |

| If following two conditions are both satisfied, the internal DMA controller reads DMA buffer at the |

| same address repeatedly and the ether MAC misunderstands it as a |

| abort may occur, though the length of actual transmitted packet is shorter than the setting of |

| LMAX0/1 (0x0f001414 / 0x0f001714) register: |

(1)The length of transmitted packet (indicated by SIZE[15:0]) is longer than the setting of DTBS bit of XMT_CFGR0/1(0x0f001600 / 0x0f001900) register and the packet length is less than 32 bytes; or the burst size set by the DTBS bit is 8 words (32 bytes) and the descriptor buffer size is 30 or 31 bytes.

(2)The physical buffer address pointer, which is indicated by transmit descriptor is not

Therefore one of the following workarounds must be implemented:

(1)Set

(2)Set

(3)Set

8 | Customer Notification |