SPRA921

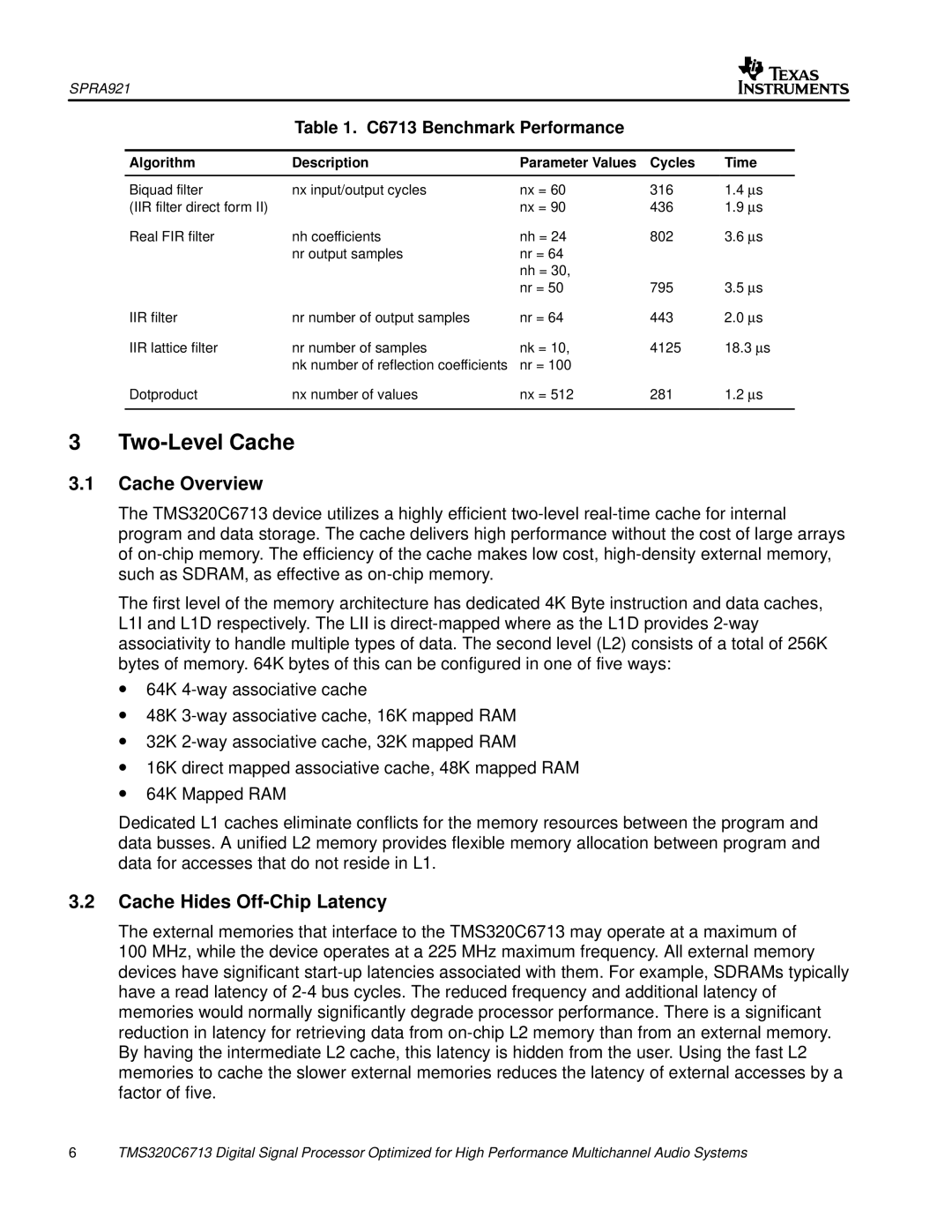

Table 1. C6713 Benchmark Performance

Algorithm | Description | Parameter Values | Cycles | Time | |

Biquad filter | nx input/output cycles | nx = 60 | 316 | 1.4 ∝ | s |

(IIR filter direct form II) |

| nx = 90 | 436 | 1.9 ∝ | s |

Real FIR filter | nh coefficients | nh = 24 | 802 | 3.6 ∝ | s |

| nr output samples | nr = 64 |

|

|

|

|

| nh = 30, |

| 3.5 ∝ |

|

|

| nr = 50 | 795 | s | |

IIR filter | nr number of output samples | nr = 64 | 443 | 2.0 ∝ | s |

IIR lattice filter | nr number of samples | nk = 10, | 4125 | 18.3 ∝ s | |

| nk number of reflection coefficients | nr = 100 |

|

|

|

Dotproduct | nx number of values | nx = 512 | 281 | 1.2 ∝ | s |

|

|

|

|

|

|

3 Two-Level Cache

3.1Cache Overview

The TMS320C6713 device utilizes a highly efficient

The first level of the memory architecture has dedicated 4K Byte instruction and data caches, L1I and L1D respectively. The LII is

•64K

•48K

•32K

•16K direct mapped associative cache, 48K mapped RAM

•64K Mapped RAM

Dedicated L1 caches eliminate conflicts for the memory resources between the program and data busses. A unified L2 memory provides flexible memory allocation between program and data for accesses that do not reside in L1.

3.2Cache Hides Off-Chip Latency

The external memories that interface to the TMS320C6713 may operate at a maximum of

100 MHz, while the device operates at a 225 MHz maximum frequency. All external memory devices have significant

6TMS320C6713 Digital Signal Processor Optimized for High Performance Multichannel Audio Systems