SCPA033

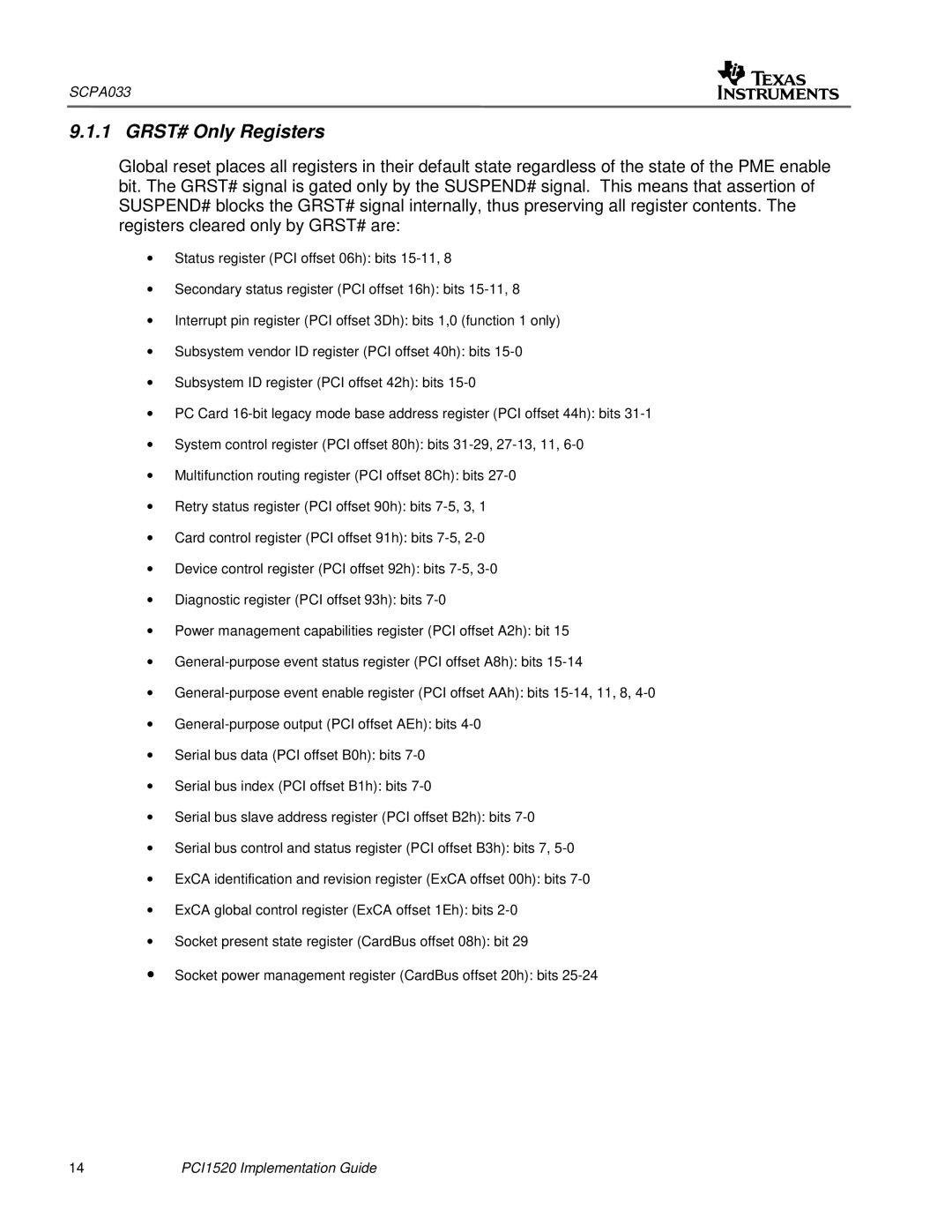

9.1.1 GRST# Only Registers

Global reset places all registers in their default state regardless of the state of the PME enable bit. The GRST# signal is gated only by the SUSPEND# signal. This means that assertion of SUSPEND# blocks the GRST# signal internally, thus preserving all register contents. The registers cleared only by GRST# are:

•Status register (PCI offset 06h): bits

•Secondary status register (PCI offset 16h): bits

•Interrupt pin register (PCI offset 3Dh): bits 1,0 (function 1 only)

•Subsystem vendor ID register (PCI offset 40h): bits

•Subsystem ID register (PCI offset 42h): bits

•PC Card

•System control register (PCI offset 80h): bits

•Multifunction routing register (PCI offset 8Ch): bits

•Retry status register (PCI offset 90h): bits

•Card control register (PCI offset 91h): bits

•Device control register (PCI offset 92h): bits

•Diagnostic register (PCI offset 93h): bits

•Power management capabilities register (PCI offset A2h): bit 15

•

•

•

•Serial bus data (PCI offset B0h): bits

•Serial bus index (PCI offset B1h): bits

•Serial bus slave address register (PCI offset B2h): bits

•Serial bus control and status register (PCI offset B3h): bits 7,

•ExCA identification and revision register (ExCA offset 00h): bits

•ExCA global control register (ExCA offset 1Eh): bits

•Socket present state register (CardBus offset 08h): bit 29

•Socket power management register (CardBus offset 20h): bits

14 | PCI1520 Implementation Guide |