SCPA033 |

|

|

|

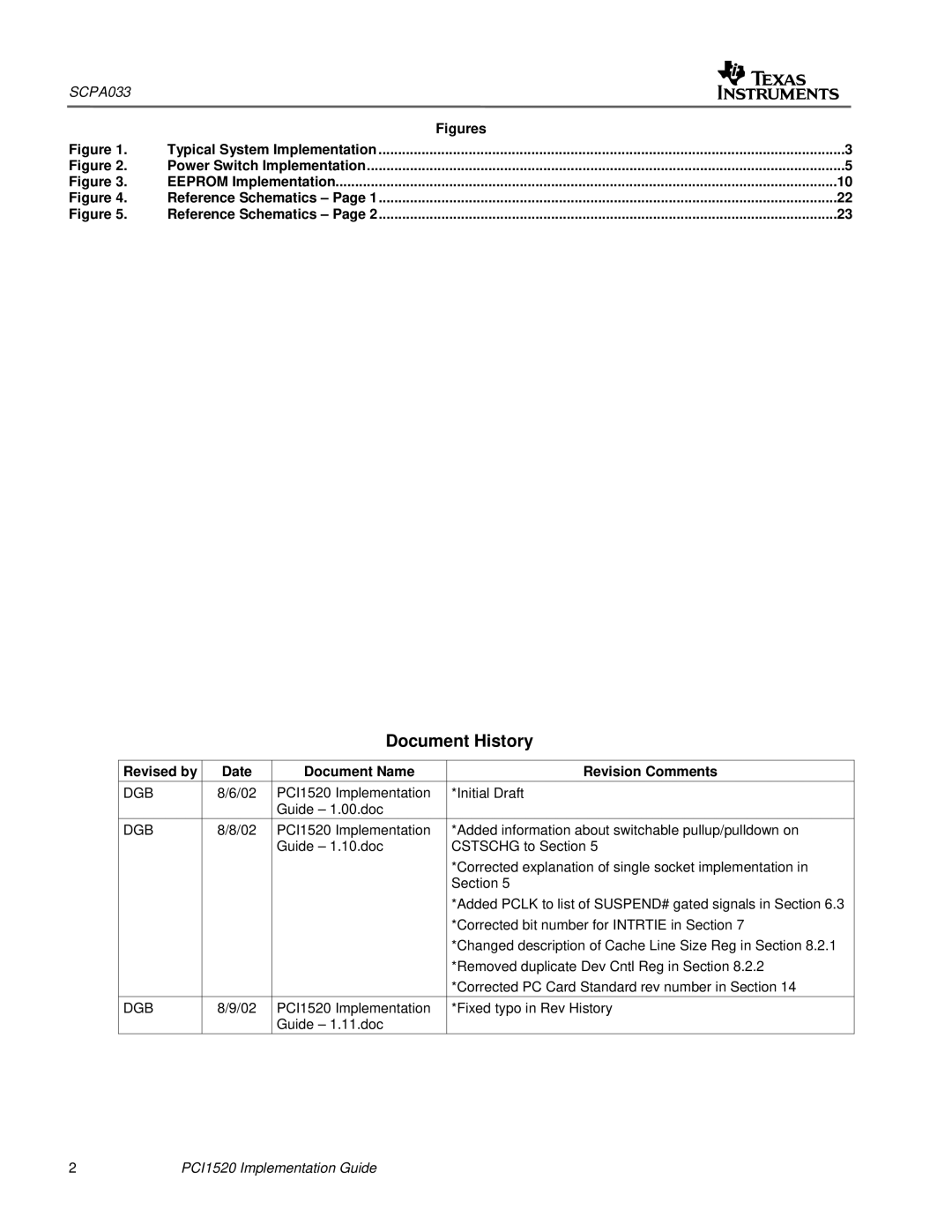

| Figures |

Figure 1. | Typical System Implementation | .......................................................................................................................3 |

Figure 2. | Power Switch Implementation | 5 |

Figure 3. | EEPROM Implementation | 10 |

Figure 4. | Reference Schematics – Page 1 | .....................................................................................................................22 |

Figure 5. | Reference Schematics – Page 2 | .....................................................................................................................23 |

Document History

Revised by | Date | Document Name | Revision Comments |

|

|

|

|

DGB | 8/6/02 | PCI1520 Implementation | *Initial Draft |

|

| Guide – 1.00.doc |

|

DGB | 8/8/02 | PCI1520 Implementation | *Added information about switchable pullup/pulldown on |

|

| Guide – 1.10.doc | CSTSCHG to Section 5 |

|

|

| *Corrected explanation of single socket implementation in |

|

|

| Section 5 |

|

|

| *Added PCLK to list of SUSPEND# gated signals in Section 6.3 |

|

|

| *Corrected bit number for INTRTIE in Section 7 |

|

|

| *Changed description of Cache Line Size Reg in Section 8.2.1 |

|

|

| *Removed duplicate Dev Cntl Reg in Section 8.2.2 |

|

|

| *Corrected PC Card Standard rev number in Section 14 |

DGB | 8/9/02 | PCI1520 Implementation | *Fixed typo in Rev History |

|

| Guide – 1.11.doc |

|

2 | PCI1520 Implementation Guide |