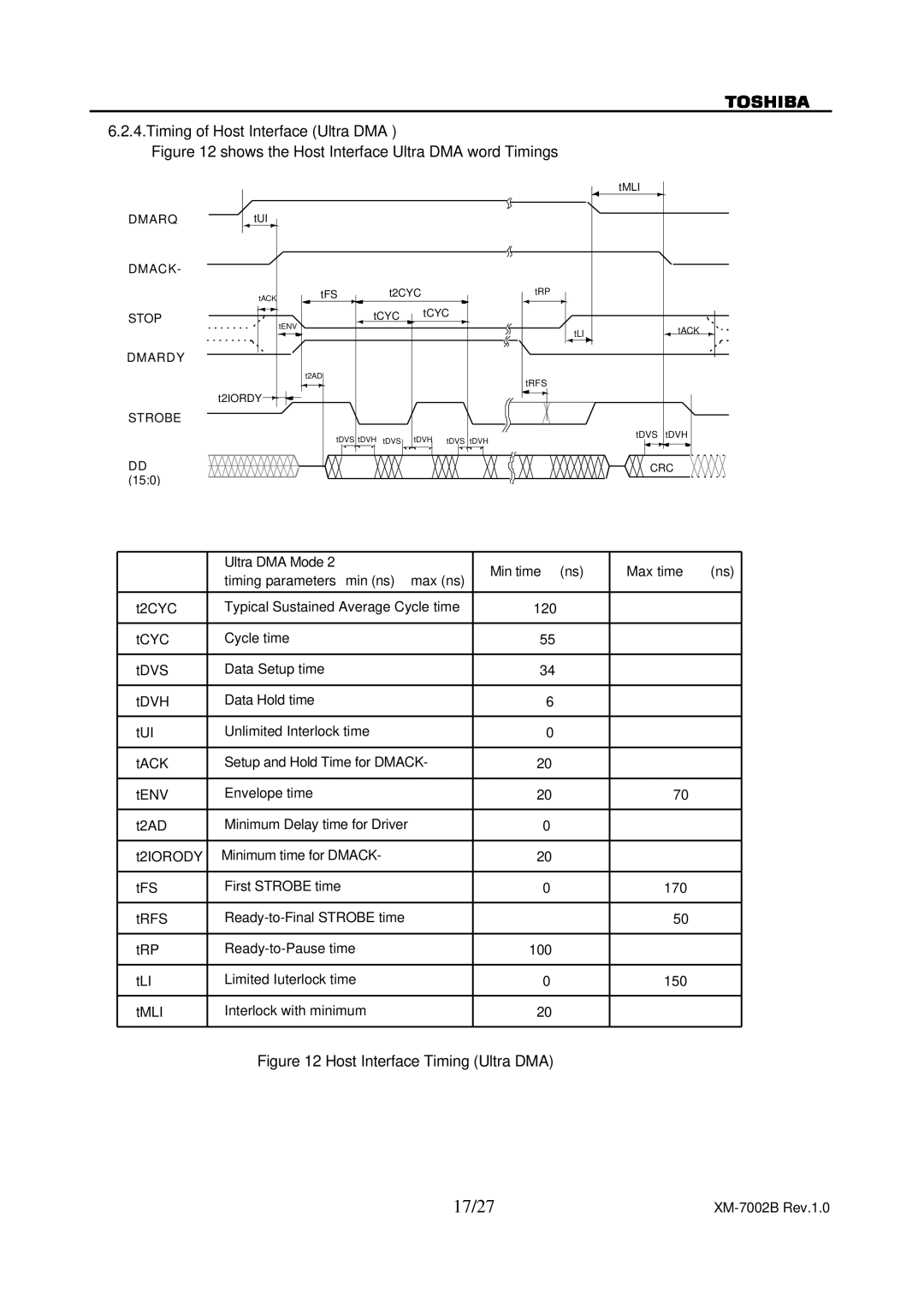

6.2.4.Timing of Host Interface (Ultra DMA )

Figure 12 shows the Host Interface Ultra DMA word Timings

DMARQ | tUI |

|

|

|

|

DMACK- |

|

|

|

|

|

| tACK | tFS | t2CYC |

| |

|

|

|

|

| |

STOP |

|

| tCYC | tCYC | |

| tENV |

|

| ||

|

|

|

|

| |

DMARDY |

|

|

|

|

|

|

| t2AD |

|

|

|

| t2IORDY |

|

|

|

|

STROBE |

|

|

|

|

|

|

| tDVS tDVH tDVS | tDVH | tDVS tDVH | |

DD |

|

|

|

|

|

(15:0) |

|

|

|

|

|

tMLI |

|

tRP |

|

tLI | tACK |

| |

tRFS |

|

tDVS | tDVH |

CRC | |

| Ultra DMA Mode 2 | Min time (ns) | Max time | (ns) |

| timing parameters min (ns) max (ns) | |||

|

|

|

| |

|

|

|

|

|

t2CYC | Typical Sustained Average Cycle time | 120 |

|

|

|

|

|

|

|

tCYC | Cycle time | 55 |

|

|

|

|

|

|

|

tDVS | Data Setup time | 34 |

|

|

|

|

|

|

|

tDVH | Data Hold time | 6 |

|

|

|

|

|

|

|

tUI | Unlimited Interlock time | 0 |

|

|

|

|

|

|

|

tACK | Setup and Hold Time for DMACK- | 20 |

|

|

|

|

|

|

|

tENV | Envelope time | 20 | 70 |

|

|

|

|

|

|

t2AD | Minimum Delay time for Driver | 0 |

|

|

|

|

|

|

|

t2IORODY | Minimum time for DMACK- | 20 |

|

|

|

|

|

|

|

tFS | First STROBE time | 0 | 170 |

|

|

|

|

|

|

tRFS |

| 50 |

| |

|

|

|

|

|

tRP | 100 |

|

| |

|

|

|

|

|

tLI | Limited Iuterlock time | 0 | 150 |

|

|

|

|

|

|

tMLI | Interlock with minimum | 20 |

|

|

|

|

|

|

|

Figure 12 Host Interface Timing (Ultra DMA)

17/27 |

|