Application Note

46959A - March 2009

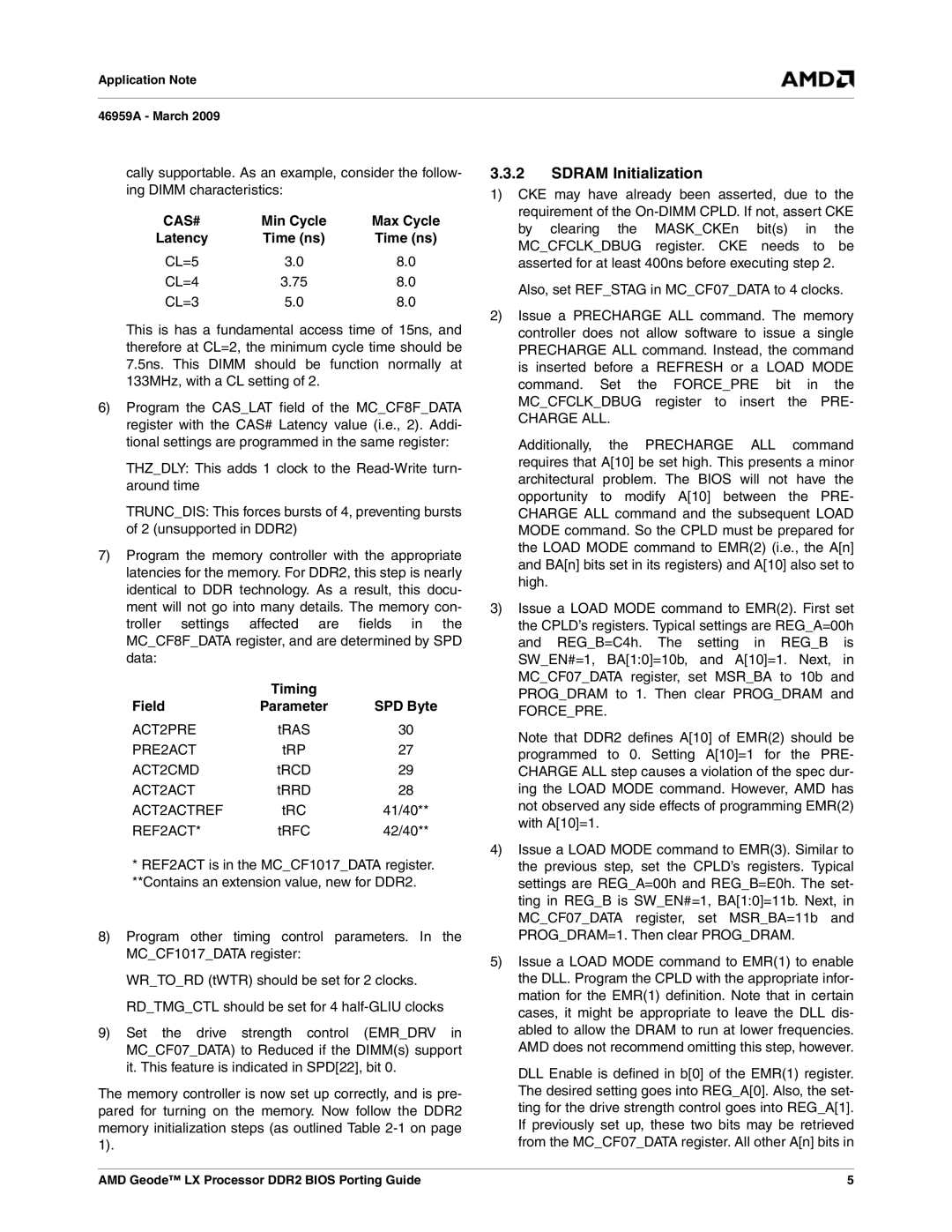

cally supportable. As an example, consider the follow- ing DIMM characteristics:

CAS# | Min Cycle | Max Cycle |

Latency | Time (ns) | Time (ns) |

CL=5 | 3.0 | 8.0 |

CL=4 | 3.75 | 8.0 |

CL=3 | 5.0 | 8.0 |

This is has a fundamental access time of 15ns, and therefore at CL=2, the minimum cycle time should be 7.5ns. This DIMM should be function normally at 133MHz, with a CL setting of 2.

6)Program the CAS_LAT field of the MC_CF8F_DATA register with the CAS# Latency value (i.e., 2). Addi- tional settings are programmed in the same register:

THZ_DLY: This adds 1 clock to the

TRUNC_DIS: This forces bursts of 4, preventing bursts of 2 (unsupported in DDR2)

7)Program the memory controller with the appropriate latencies for the memory. For DDR2, this step is nearly identical to DDR technology. As a result, this docu- ment will not go into many details. The memory con- troller settings affected are fields in the MC_CF8F_DATA register, and are determined by SPD data:

| Timing |

|

Field | Parameter | SPD Byte |

ACT2PRE | tRAS | 30 |

PRE2ACT | tRP | 27 |

ACT2CMD | tRCD | 29 |

ACT2ACT | tRRD | 28 |

ACT2ACTREF | tRC | 41/40** |

REF2ACT* | tRFC | 42/40** |

*REF2ACT is in the MC_CF1017_DATA register. **Contains an extension value, new for DDR2.

8)Program other timing control parameters. In the MC_CF1017_DATA register:

WR_TO_RD (tWTR) should be set for 2 clocks. RD_TMG_CTL should be set for 4

9)Set the drive strength control (EMR_DRV in MC_CF07_DATA) to Reduced if the DIMM(s) support it. This feature is indicated in SPD[22], bit 0.

The memory controller is now set up correctly, and is pre- pared for turning on the memory. Now follow the DDR2 memory initialization steps (as outlined Table

3.3.2SDRAM Initialization

1)CKE may have already been asserted, due to the requirement of the

Also, set REF_STAG in MC_CF07_DATA to 4 clocks.

2)Issue a PRECHARGE ALL command. The memory controller does not allow software to issue a single PRECHARGE ALL command. Instead, the command is inserted before a REFRESH or a LOAD MODE command. Set the FORCE_PRE bit in the MC_CFCLK_DBUG register to insert the PRE-

CHARGE ALL.

Additionally, the PRECHARGE ALL command requires that A[10] be set high. This presents a minor architectural problem. The BIOS will not have the opportunity to modify A[10] between the PRE- CHARGE ALL command and the subsequent LOAD MODE command. So the CPLD must be prepared for the LOAD MODE command to EMR(2) (i.e., the A[n] and BA[n] bits set in its registers) and A[10] also set to high.

3)Issue a LOAD MODE command to EMR(2). First set the CPLD’s registers. Typical settings are REG_A=00h and REG_B=C4h. The setting in REG_B is SW_EN#=1, BA[1:0]=10b, and A[10]=1. Next, in MC_CF07_DATA register, set MSR_BA to 10b and PROG_DRAM to 1. Then clear PROG_DRAM and FORCE_PRE.

Note that DDR2 defines A[10] of EMR(2) should be programmed to 0. Setting A[10]=1 for the PRE- CHARGE ALL step causes a violation of the spec dur- ing the LOAD MODE command. However, AMD has not observed any side effects of programming EMR(2) with A[10]=1.

4)Issue a LOAD MODE command to EMR(3). Similar to the previous step, set the CPLD’s registers. Typical settings are REG_A=00h and REG_B=E0h. The set- ting in REG_B is SW_EN#=1, BA[1:0]=11b. Next, in MC_CF07_DATA register, set MSR_BA=11b and PROG_DRAM=1. Then clear PROG_DRAM.

5)Issue a LOAD MODE command to EMR(1) to enable the DLL. Program the CPLD with the appropriate infor- mation for the EMR(1) definition. Note that in certain cases, it might be appropriate to leave the DLL dis- abled to allow the DRAM to run at lower frequencies. AMD does not recommend omitting this step, however.

DLL Enable is defined in b[0] of the EMR(1) register. The desired setting goes into REG_A[0]. Also, the set- ting for the drive strength control goes into REG_A[1]. If previously set up, these two bits may be retrieved from the MC_CF07_DATA register. All other A[n] bits in

AMD Geode™ LX Processor DDR2 BIOS Porting Guide | 5 |