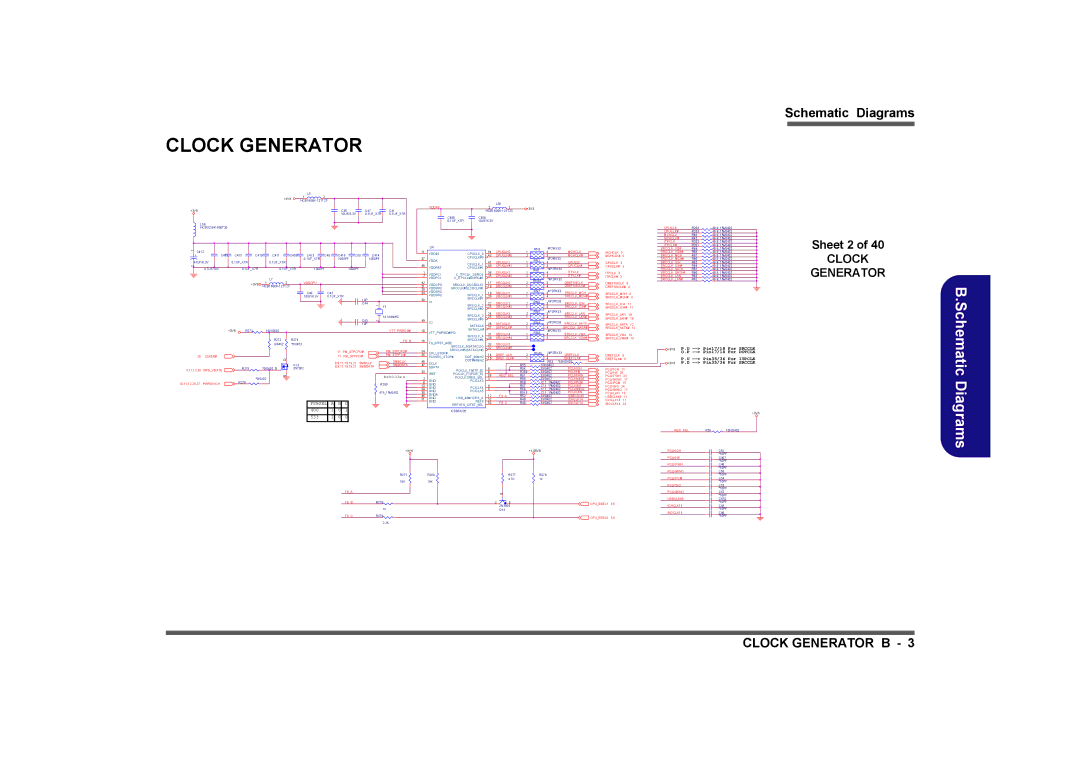

CLOCK GENERATOR

Schematic Diagrams

|

| L8 |

|

|

+3VS | 1 | 2 |

|

|

|

| |||

|

|

| ||

+3VS |

| C39 | C47 | C41 |

|

| 10UF/6.3V | 0.1UF_X7R | 0.1UF_X7R |

L58 |

|

|

|

|

|

|

|

| |

1 | C412 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| + | C417 | C415 | C410 | C411 | C409 | C413 | C49 | C416 | C50 | C414 |

| |

| 47UF/6.3V |

| 0.1UF_X7R |

| 0.1UF_X7R | 0.1UF_X7R |

| 1000PF | 1000PF |

| |||

2 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 4.7UF/10V |

| 0.1UF_X7R |

| 0.1UF_X7R | 1000PF |

| 1000PF |

|

| |||

|

|

|

|

|

| L7 |

|

|

|

|

|

|

|

|

|

|

| +3VS |

| 1 | 2 | VDDCPU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| C40 | C42 |

|

|

|

|

|

|

|

|

|

|

|

| 10UF/6.3V | 0.1UF_X7R | 10P |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| C44 | 1 | Y1 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| C43 |

| 14.318MHZ |

|

|

|

|

|

|

|

|

|

|

| 2 |

| |

|

|

|

|

|

|

|

|

|

|

| 10P |

|

|

|

| +3VS | R273 |

| 10K/0402 |

|

|

|

|

|

| VTT_PWRGD# | |

|

|

|

|

| L56 |

|

|

|

|

|

|

|

| VDD48 |

|

| 2 | 1 | +3VS |

|

|

|

|

| |

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| ||

|

| C408 | C406 |

|

|

|

|

|

|

|

| |

|

| 0.1UF_X7R | 10UF/6.3V |

|

|

|

|

|

|

|

| |

| U4 |

|

|

|

|

| RN3 | 4P2RX33 |

|

|

|

|

11 | VDD48 |

| CPUCLK_0 | 44 | CPUCLK0 | 1 |

| 4 | MCHCLK | MCHCLK | 5 |

|

|

|

| CPUCLK#0 | 43 | CPUCLK#0 | 2 |

| 3 | MCHCLK# | MCHCLK# | 5 |

|

37 | VDDA |

|

|

|

| RN2 | 4P2RX33 |

|

|

|

| |

|

| CPUCLK_1 | 41 | CPUCLK1 | 1 | 4 | CPUCLK | CPUCLK | 3 |

| ||

48 | VDDREF |

| 40 | CPUCLK#1 | 2 |

| 3 | CPUCLK# | CPUCLK# | 3 |

| |

| CPUCLK#1 |

|

| |||||||||

|

|

|

|

| RN1 | *4P2RX33 |

|

|

|

| ||

1 |

|

|

| 36 | CPUCLK2 | 1 | 4 | ITPCLK | ITPCLK 3 |

|

| |

VDDPCI | C_ITPCLK_2/SRC6 |

|

|

| ||||||||

7 | 35 | CPUCLK#2 | 2 |

| 3 | ITPCLK# | ITPCLK# | 3 |

| |||

VDDPCI | C_ITPCLK#2/SRC#6 |

|

| |||||||||

|

|

|

| RN39 | *4P2RX33 |

|

|

|

| |||

42 |

|

|

| 17 | SRCCLK0 | 2 | 3 | DREFSSCLK | DREFSSCLK 6 | |||

VDDCPU | SRCCLK_0(LCDCLK) |

| ||||||||||

21 | 18 | SRCCLK#0 | 1 |

| 4 | DREFSSCLK# | DREFSSCLK# | 6 | ||||

VDDSRC | SRCCLK#0(LCDCLK#) |

| ||||||||||

28 |

|

|

| RN7 | 34P2RX33 |

|

|

|

| |||

VDDSRC |

|

|

| SRCCLK1 |

| SRCCLK_MCH |

|

|

| |||

34 |

| SRCCLK_1 | 19 | 2 | SRCCLK_MCH | 6 | ||||||

| VDDSRC |

| 20 | SRCCLK#1 | 1 |

| 4 | SRCCLK_MCH# | SRCCLK_MCH# 6 | |||

50 |

|

| SRCCLK#1 |

| ||||||||

X1 |

|

|

|

| RN6 | 34P2RX33 |

|

|

|

| ||

|

| SRCCLK_2 | 22 | SRCCLK2 | 2 | SRCCLK_ICH | SRCCLK_ICH | 11 | ||||

|

|

| 23 | SRCCLK#2 | 1 |

| 4 | SRCCLK_ICH# | SRCCLK_ICH# | 11 | ||

|

|

| SRCCLK#2 |

| ||||||||

|

|

|

|

|

| RN5 | 34P2RX33 |

|

|

|

| |

|

|

| SRCCLK_3 | 24 | SRCCLK3 | 2 | SRCCLK_LAN | SRCCLK_LAN | 19 | |||

|

|

| 25 | SRCCLK#3 | 1 |

| 4 | SRCCLK_LAN# | ||||

49 |

|

| SRCCLK#3 |

| SRCCLK_LAN# | 19 | ||||||

X2 |

|

|

|

| RN4 | 34P2RX33 |

| |||||

|

| 26 | SATACLK | 2 | SRCCLK_SATA |

|

|

| ||||

|

| SATACLK | SRCCLK_SATA | 12 | ||||||||

|

|

| 27 | SATACLK# | 1 |

| 4 | SRCCLK_SATA# | SRCCLK_SATA# 12 | |||

10 |

|

| SATACLK# |

| ||||||||

VTT_PWRGD#/PD |

|

|

| RN8 | 4P2RX33 |

|

|

|

| |||

| SRCCLK_4 | 31 | SRCCLK4 | 1 | 4 | SRCCLK_VGA | SRCCLK_VGA | 10 | ||||

|

|

|

| |||||||||

CPUCLK | R284 | 49.9_1%/0402 | |||

|

|

|

|

|

|

CPUCLK# | R283 |

| 49.9_1%/0402 | ||

|

|

|

|

|

|

MCHCLK | R46 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

MCHCLK# | R45 |

| 49.9_1%/0402 | ||

|

|

|

|

|

|

ITPCLK | R282 |

| 49.9_1%/0402 | ||

|

|

|

|

|

|

ITPCLK# | R281 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_VGA | R69 |

| 49.9_1%/0402 | ||

|

|

|

|

|

|

SRCCLK_VGA# | R68 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_MCH | R67 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_MCH# | R66 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_ICH | R65 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_ICH# | R64 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_SATA | R61 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_SATA# | R60 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_LAN | R63 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

SRCCLK_LAN# | R62 |

|

| 49.9_1%/0402 | |

|

|

|

|

|

|

Sheet 2 of 40

CLOCK

GENERATOR

B.

30 SRCCLK#4 | 2 | 3 | SRCCLK_VGA# |

|

|

| R272 |

|

|

| 0/0402 |

26 | CLKEN# |

| D |

|

|

| |

6,11,12,26 | DPG_VGATE | R275 | *0/0402 G |

|

| ||

|

|

| S |

|

| R276 | *0/0402 |

10,11,12,26,27 | PWROKICH |

| |

|

|

R274 |

|

| FS_B | |

*0/0402 |

|

| ||

|

|

| ||

| 11 PM_STPCPU# | PM_STPCPU# | ||

| 11 PM_STPPCI# | PM_STPPCI# | ||

|

| |||

| 8,9,11,18,19,21 | SMBCLK | SMBCLK | |

Q13 | SMBDATA | |||

8,9,11,18,19,21 | SMBDATA | |||

2N7002 |

| |||

|

|

| ||

|

|

| Iref=2.32mA | |

|

|

| R280 | |

|

|

| 475_1%/0402 | |

16 |

|

| SRCCLK#4 |

|

|

|

|

|

| SRCCLK_VGA# 10 | ||

FS_B/TST_MDE |

| 33 | SRCCLK5 |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||||

|

| SRCCLK_5(SATACLK) | 32 SRCCLK#5 |

|

|

|

|

|

|

| ||

54 | CPU_STOP# | SRCCLK#5(SATACLK#) |

|

|

| RN40 3*4P2RX33 |

|

|

|

| ||

55 |

| DOT_96MHZ | 14 | DREF_CLK | 2 | DREFCLK | DREFCLK | 6 | ||||

| PCI/SRC_STOP# | 15 | DREF_CLK# | 1 | 4 |

| DREFCLK# | DREFCLK# | 6 | |||

46 |

|

| DOT#96MHZ |

|

|

| R53 | *10K/0402 | ||||

SCLK |

|

|

|

|

|

|

| |||||

47 |

|

|

|

| R55 | 10K/0402 |

|

|

|

|

| |

SDATA |

|

|

|

|

|

|

|

|

| |||

|

| PCICLK_F0(ITP_E) | 8 |

| R54 | 33/0402 |

| PCLKICH | PCLKICH | 11 | ||

|

|

|

|

| ||||||||

39 |

|

| 9 |

| R268 | 33/0402 |

| PCLKH8 | PCLKH8 | 25 | ||

IREF | PCICLK_F1(PCIE_E) |

|

| |||||||||

| 56 | REQ_SEL | R51 | 33/0402 |

| PCLKFWH | PCLKFWH | 24 | ||||

|

|

| PCICLK2/REQ_SEL |

| ||||||||

2 |

|

| 3 |

| R59 | 33/0402 |

| PCLKMINI1 | PCLKMINI1 | 17 | ||

GND |

| PCICLK3 |

|

| ||||||||

6 |

|

|

| R58 | 12.1_1%/0402 | PCLKPCM | PCLKPCM 15 | |||||

GND |

|

|

|

| ||||||||

13 |

|

| 4 |

| R57 | 12.1_1%/0402 | PCLKSIO | PCLKSIO | 24 | |||

GND |

| PCICLK4 |

| |||||||||

29 |

| 5 |

| R56 | 12.1_1%/0402 | PCLKMINI2 | PCLKMINI2 | 17 | ||||

GND |

| PCICLK5 |

| |||||||||

38 |

|

|

| R515 | 12.1_1%/0402 | PCLKLAN | PCLKLAN |

| 18 | |||

GNDA |

|

|

|

|

| |||||||

45 |

|

| 12 | FS_A | R52 | 33/0402 |

| USBCLK48 | USBCLK48 | 11 | ||

|

|

|

| |||||||||

FSBSEL | A | B | C |

400 | 1 | 0 | 1 |

533 | 1 | 0 | 0 |

+3VS

51 | GND | USB_48MHZ/FS_A | 52 |

| R48 | 33/0402 | ICHCLK14 | ICHCLK14 | 11 |

GND | REF0 |

| |||||||

| 53 | FS_C | R49 | 33/0402 | SIOCLK14 | SIOCLK14 | 24 | ||

|

| REF1/FS_C/TST_SEL | |||||||

|

|

|

|

|

|

| |||

|

| ICS954226 |

|

|

|

|

|

|

|

|

|

|

|

|

| +1.05VS |

|

|

|

| R271 | R269 | R277 | R278 |

|

| 10K | 10K | 4.7K | 1K |

|

|

|

|

| ||

FS_A |

|

| B |

|

|

FS_B | R270 | C | E | CPU_BSEL1 | 3,6 |

|

|

| 2N3904 | ||

| 1K |

|

|

| |

|

| Q14 |

|

| |

FS_C | R279 |

|

| CPU_BSEL0 | 3,6 |

|

|

|

| ||

| 2.2K |

|

|

|

|

+3VS P.U --> Pin17/18 For SRCCLK

O.P --> Pin17/18 For DOTCLK

P.U --> Pin35/36 For ITPCLK +3VS P.D --> Pin35/36 For SRCCLK

+3VS

REQ_SEL | R50 |

|

| 10K/0402 |

|

| |

|

|

|

|

|

|

|

|

PCLKICH |

|

| C51 |

| |||

|

|

| *10PF |

| |||

PCLKH8 |

|

| C407 |

| |||

|

|

| *10PF |

| |||

PCLKFWH |

|

| C48 |

| |||

|

|

| *10PF |

| |||

PCLKMINI1 |

|

| C55 |

| |||

|

|

| *10PF |

| |||

PCLKPCM |

|

| C54 |

| |||

|

|

| *10PF |

| |||

PCLKSIO |

|

| C53 |

| |||

|

|

| *10PF |

| |||

PCLKMINI2 |

|

| C52 |

| |||

USBCLK48 |

|

| *10PF |

| |||

|

| C670 |

| ||||

|

|

| *10PF |

| |||

ICHCLK14 |

|

| C45 |

| |||

|

|

| *10PF |

| |||

SIOCLK14 |

|

| C46 |

| |||

|

|

| *10PF |

|

| ||

Schematic Diagrams

CLOCK GENERATOR B - 3