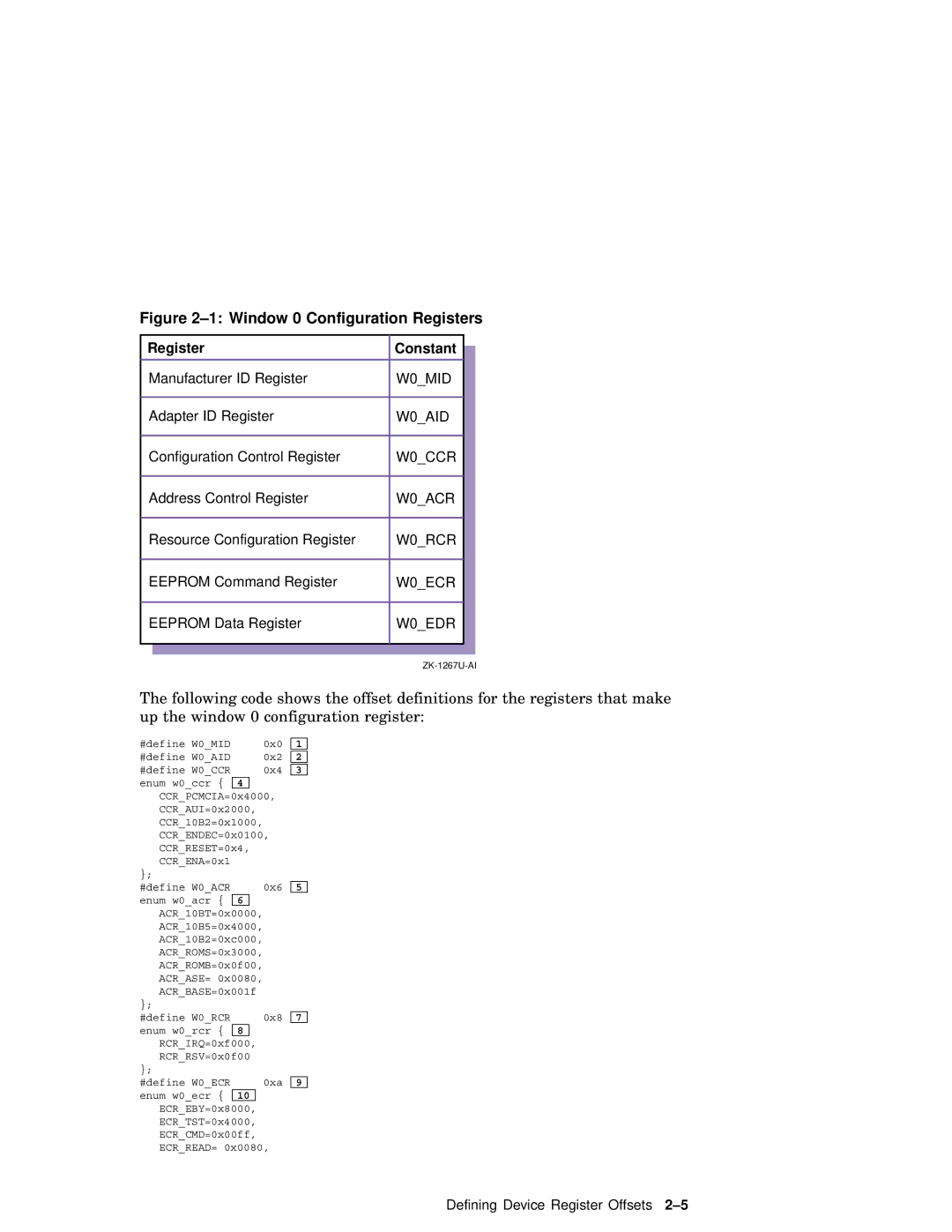

Figure 2–1: Window 0 Configuration Registers

Register | Constant |

|

|

|

|

Manufacturer ID Register | W0_MID |

|

|

|

|

Adapter ID Register | W0_AID |

|

|

|

|

Configuration Control Register | W0_CCR |

|

|

|

|

Address Control Register | W0_ACR |

|

|

|

|

Resource Configuration Register | W0_RCR |

|

|

|

|

EEPROM Command Register | W0_ECR |

|

|

|

|

EEPROM Data Register | W0_EDR |

|

|

|

|

The following code shows the offset definitions for the registers that make up the window 0 configuration register:

#define W0_MID |

| 0x0 | |

#define | W0_AID |

| 0x2 |

#define | W0_CCR |

| 0x4 |

enum w0_ccr { | 4 |

| |

CCR_PCMCIA=0x4000, CCR_AUI=0x2000, CCR_10B2=0x1000, CCR_ENDEC=0x0100, CCR_RESET=0x4, CCR_ENA=0x1

};

#define W0_ACR 0x6 enum w0_acr { 6

ACR_10BT=0x0000,

ACR_10B5=0x4000,

ACR_10B2=0xc000,

ACR_ROMS=0x3000,

ACR_ROMB=0x0f00,

ACR_ASE= 0x0080,

ACR_BASE=0x001f

};

#define W0_RCR 0x8 enum w0_rcr { 8

RCR_IRQ=0xf000,

RCR_RSV=0x0f00

};

#define W0_ECR 0xa enum w0_ecr { 10

ECR_EBY=0x8000,

ECR_TST=0x4000,

ECR_CMD=0x00ff,

ECR_READ= 0x0080,

1

2

3

5

7

9