ASI_RSIZE8 | Indicates a RAM size of 8 kilobytes (the default). |

ASI_RSIZE32 Indicates a RAM size of 32 kilobytes.

2.5 Window 1 Operational Register Offset Definitions

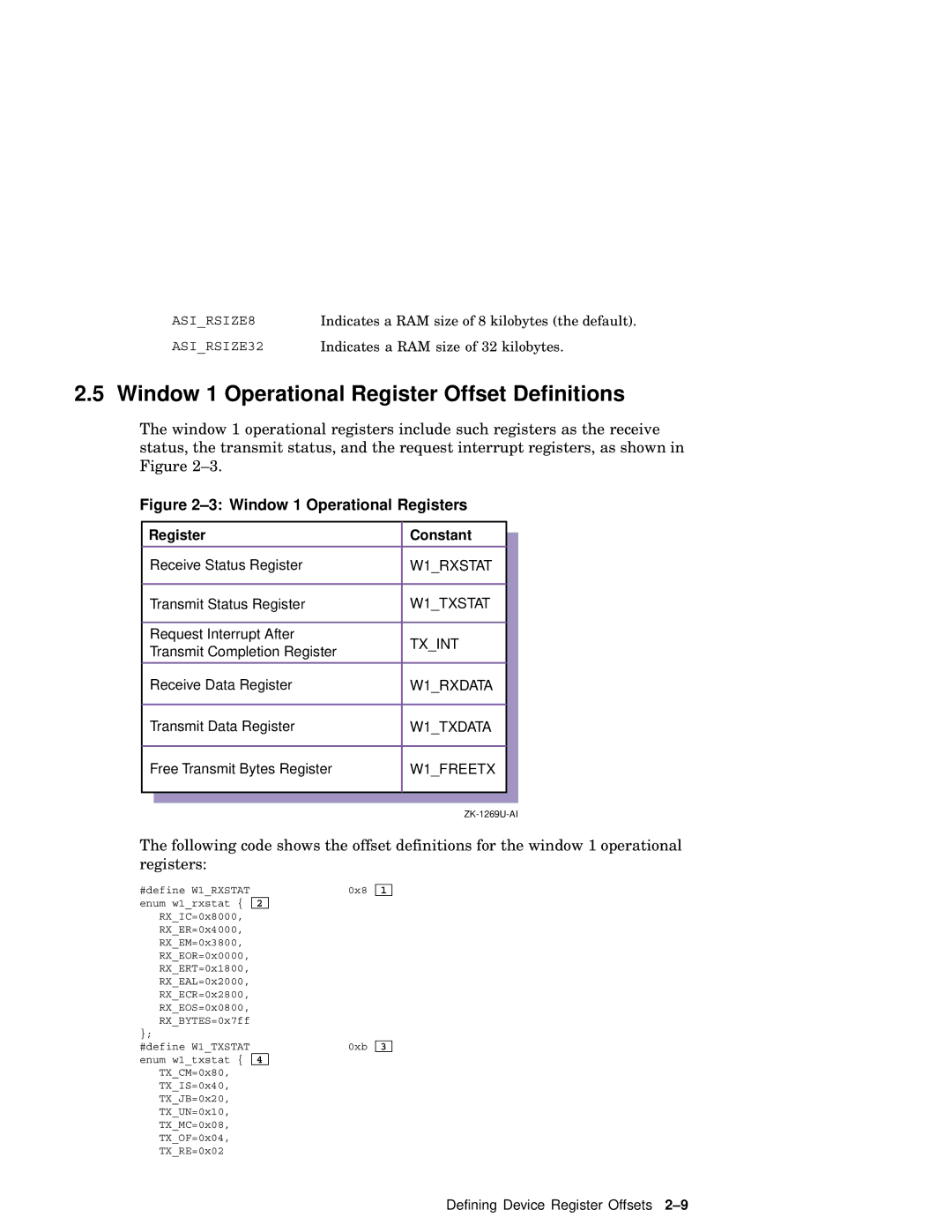

The window 1 operational registers include such registers as the receive status, the transmit status, and the request interrupt registers, as shown in Figure

Figure 2–3: Window 1 Operational Registers

Register | Constant | |

Receive Status Register | W1_RXSTAT | |

|

| |

Transmit Status Register | W1_TXSTAT | |

|

| |

Request Interrupt After | TX_INT | |

Transmit Completion Register | ||

|

Receive Data Register

W1_RXDATA

Transmit Data Register

W1_TXDATA

Free Transmit Bytes Register

W1_FREETX

The following code shows the offset definitions for the window 1 operational registers:

#define W1_RXSTAT enum w1_rxstat { RX_IC=0x8000, RX_ER=0x4000, RX_EM=0x3800,

RX_EOR=0x0000, RX_ERT=0x1800, RX_EAL=0x2000, RX_ECR=0x2800, RX_EOS=0x0800, RX_BYTES=0x7ff

};

#define W1_TXSTAT enum w1_txstat { TX_CM=0x80, TX_IS=0x40, TX_JB=0x20, TX_UN=0x10, TX_MC=0x08, TX_OF=0x04, TX_RE=0x02

0x8

2

0xb

4

1

3