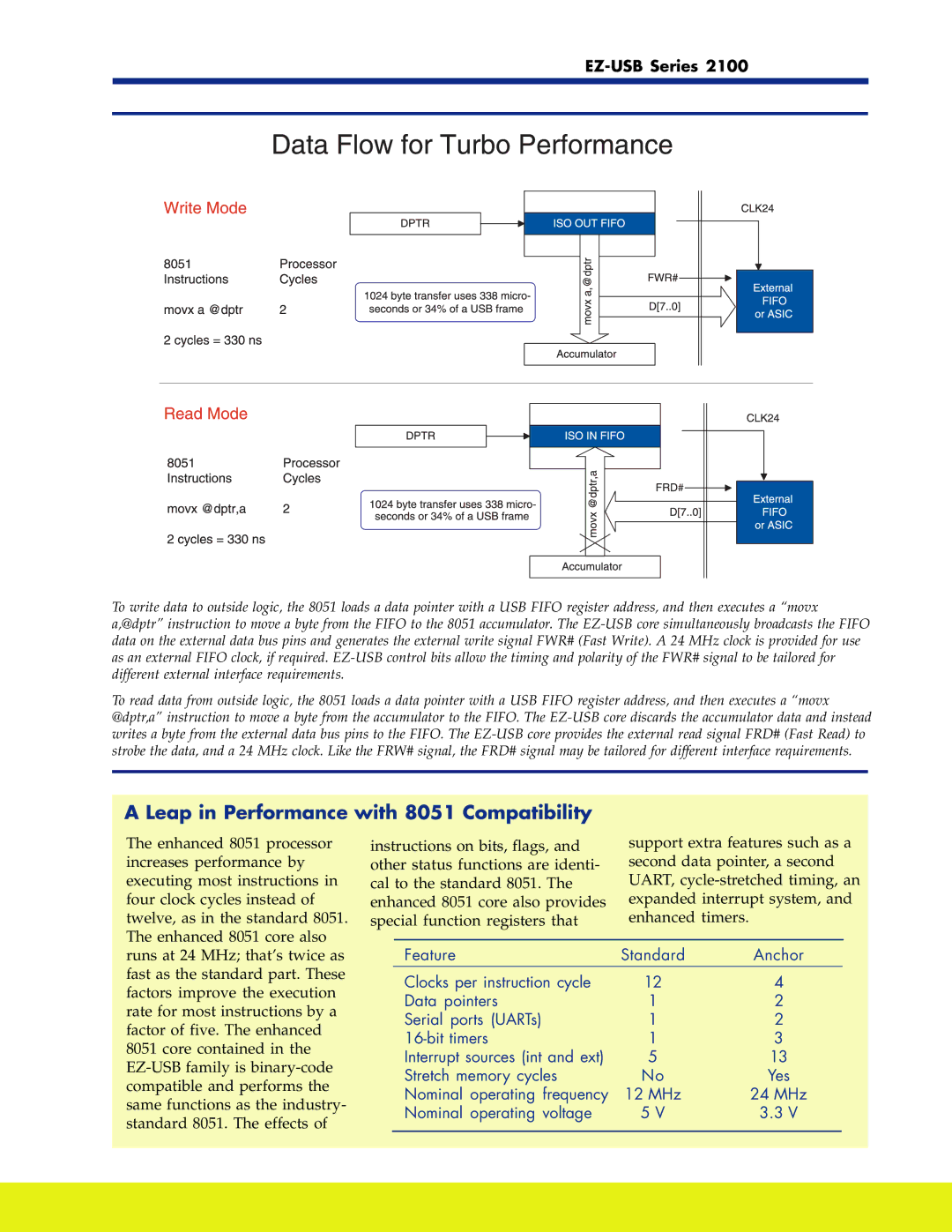

To write data to outside logic, the 8051 loads a data pointer with a USB FIFO register address, and then executes a “movx a,@dptr” instruction to move a byte from the FIFO to the 8051 accumulator. The

To read data from outside logic, the 8051 loads a data pointer with a USB FIFO register address, and then executes a “movx @dptr,a” instruction to move a byte from the accumulator to the FIFO. The

A Leap in Performance with 8051 Compatibility

The enhanced 8051 processor increases performance by executing most instructions in four clock cycles instead of twelve, as in the standard 8051. The enhanced 8051 core also runs at 24 MHz; that’s twice as fast as the standard part. These factors improve the execution rate for most instructions by a factor of five. The enhanced 8051 core contained in the

instructions on bits, flags, and | support extra features such as a | ||||

other status functions are identi- | second data pointer, a second | ||||

cal to the standard 8051. The | UART, | ||||

enhanced 8051 core also provides | expanded interrupt system, and | ||||

special function registers that | enhanced timers. |

|

| ||

|

|

|

|

|

|

|

| Feature | Standard | Anchor | |

|

| Clocks per instruction cycle | 12 | 4 |

|

|

| Data pointers | 1 | 2 |

|

|

| Serial ports (UARTs) | 1 | 2 |

|

|

| 1 | 3 |

| |

|

| Interrupt sources (int and ext) | 5 | 13 |

|

|

| Stretch memory cycles | No | Yes | |

|

| Nominal operating frequency | 12 MHz | 24 MHz | |

|

| Nominal operating voltage | 5 V | 3.3 V | |

|

|

|

|

|

|