CY7C1019CV33

128K x 8 Static RAM

Features

•Pin and function compatible with CY7C1019BV33

•High speed

— tAA = 10 ns

•CMOS for optimum speed/power

•Data retention at 2.0V

•Center power/ground pinout

•Automatic

•Easy memory expansion with CE and OE options

•Available in

Functional Description

The CY7C1019CV33 is a

device has an automatic

Writing to the device is accomplished by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. Data on the eight I/O pins (I/O0 through I/O7) is then written into the location specified on the address pins (A0 through A16).

Reading from the device is accomplished by taking Chip Enable (CE) and Output Enable (OE) LOW while forcing Write Enable (WE) HIGH. Under these conditions, the contents of the memory location specified by the address pins will appear on the I/O pins.

The eight input/output pins (I/O0 through I/O7) are placed in a

The CY7C1019CV33 is available in Standard

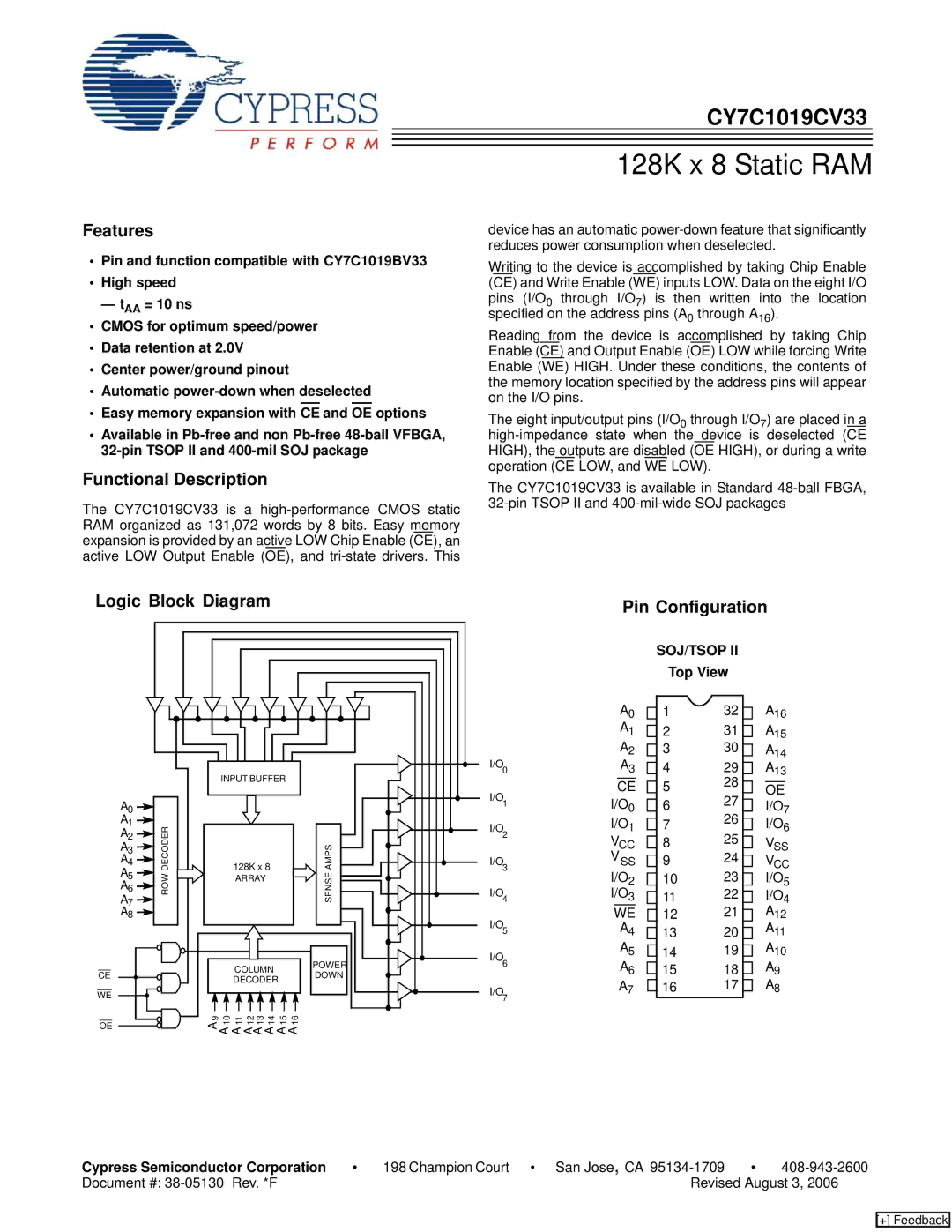

Logic Block Diagram |

|

| |||

|

| INPUT BUFFER |

| I/O0 | |

|

|

|

| ||

A0 |

|

|

|

| I/O1 |

A1 | DECODER |

|

|

| I/O2 |

A |

| 128K x 8 | AMPS | ||

A43 |

| I/O3 | |||

2 |

|

|

|

|

|

A |

|

|

| SENSE |

|

A7 | ROW |

| ARRAY | I/O4 | |

A5 |

|

|

|

| |

A6 |

|

|

|

|

|

A8 |

|

|

|

| I/O5 |

|

|

|

|

| |

|

|

| COLUMN | POWER | I/O6 |

CE |

|

| DOWN |

| |

|

| DECODER |

| ||

|

|

|

| I/O7 | |

WE |

|

|

|

| |

OE | 9 | 10 | 11 12 13 14 15 16 |

|

|

A A A A A A A A |

|

| |||

|

|

| |||

Pin Configuration

SOJ/TSOP II

Top View

A0 | 1 | 32 | A16 |

A1 | 2 | 31 | A15 |

A2 | 3 | 30 | A |

A3 |

|

| 14 |

4 | 29 | A | |

CE | 5 | 28 | 13 |

OE | |||

I/O0 | 6 | 27 | I/O |

|

| 26 | 7 |

I/O1 | 7 | I/O6 | |

VCC | 8 | 25 | V |

VSS |

| 24 | SS |

9 | VCC | ||

I/O2 | 10 | 23 | I/O5 |

I/O3 | 11 | 22 | I/O |

|

| 4 | |

WE | 12 | 21 | A12 |

A4 | 13 | 20 | A11 |

A5 | 14 | 19 | A10 |

A6 | 15 | 18 | A9 |

A7 | 16 | 17 | A8 |

Cypress Semiconductor Corporation | • | 198 Champion Court • San Jose, CA | • | |

Document #: |

| Revised August 3, 2006 | ||

[+] Feedback