CY7C1007B, CY7C107B specifications

Cypress Semiconductor's CY7C107B and CY7C1007B are high-performance static random-access memory (SRAM) devices designed for demanding applications that require fast access times, low power consumption, and high reliability. Both of these memory chips are particularly suitable for use in a variety of electronic systems, including telecommunications, networking, industrial automation, and consumer electronics.The CY7C107B is a 1 megabit SRAM, while the CY7C1007B is a larger 256 kilobit SRAM. They belong to the Cypress family of asynchronous SRAMs, which are known for their ease of integration into existing systems. One of the main features of these devices is their high-speed operation, with access times that can be as low as 10 nanoseconds. This rapid access allows for quick read and write cycles, making them ideal for applications where speed is critical.

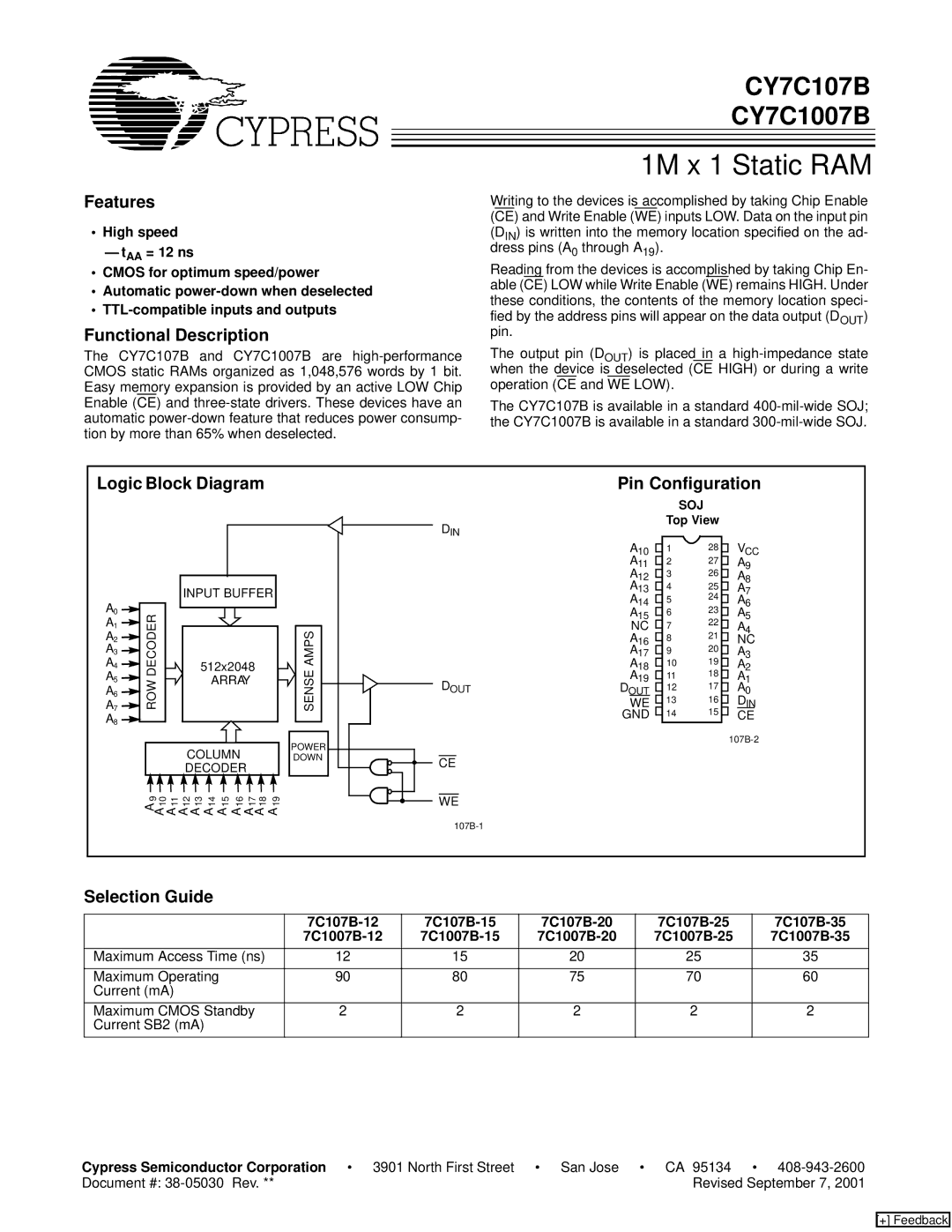

Both memory chips are available in a variety of package options, including 28-pin DIP and 32-pin SOP, allowing for flexible use in different system designs. The CY7C107B and CY7C1007B also employ a dual-port architecture, which enhances their functionality by allowing multiple devices or processors to access the memory simultaneously without conflict. This characteristic is especially beneficial in systems requiring high-throughput data handling, such as video processing or high-speed networking.

Power consumption is another significant aspect of these SRAM devices. They are designed to operate efficiently, with low standby current and minimal active power usage. This makes them suitable for battery-powered and energy-sensitive applications, helping to extend the operating life of such devices.

In terms of reliability, the CY7C107B and CY7C1007B are built using advanced CMOS technology, which not only enhances performance but also increases durability and longevity. These SRAMs are capable of withstanding environmental stresses, thus ensuring consistent performance over time. Furthermore, they incorporate built-in data integrity features to protect against soft errors caused by radiation or other disturbances.

Overall, the Cypress CY7C107B and CY7C1007B SRAMs are robust and efficient solutions for high-speed memory needs. Their combination of fast access times, low power consumption, dual-port capabilities, and reliability makes them excellent choices for a wide range of applications in a rapidly evolving tech landscape. With their proven performance in various sectors, these memory chips continue to be a popular choice among engineers and designers seeking reliable memory solutions.