|

|

|

|

|

|

|

|

|

| CY7C1411BV18, CY7C1426BV18 | |

|

|

|

|

|

|

|

|

|

| CY7C1413BV18, CY7C1415BV18 | |

|

|

|

|

|

|

|

|

|

| ||

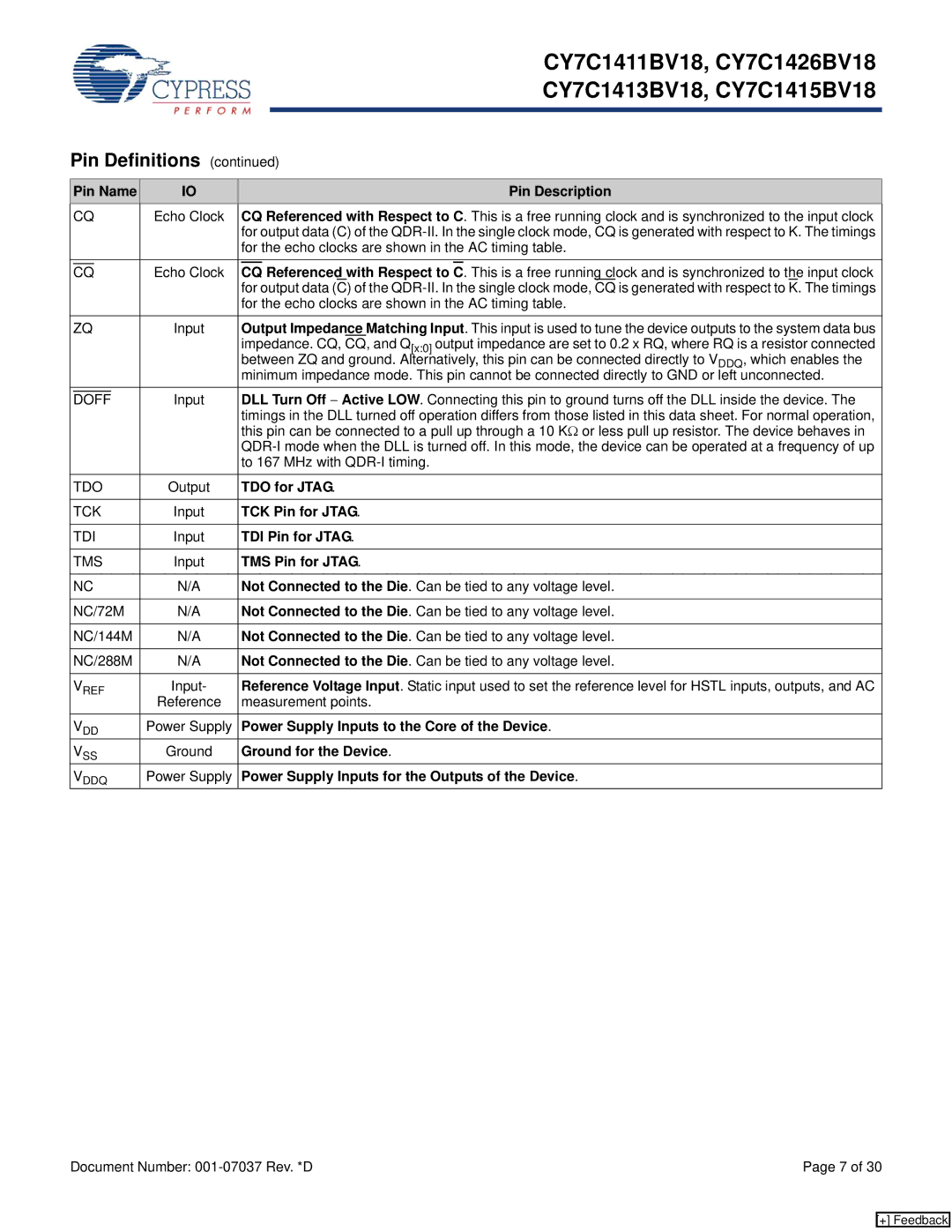

Pin Definitions (continued) | |||||||||||

|

|

|

|

|

|

|

|

| |||

| Pin Name | IO |

|

|

|

|

| Pin Description | |||

| CQ | Echo Clock | CQ Referenced with Respect to C. This is a free running clock and is synchronized to the input clock | ||||||||

|

|

|

|

| for output data (C) of the | ||||||

|

|

|

|

| for the echo clocks are shown in the AC timing table. | ||||||

|

|

|

| Echo Clock |

| Referenced with Respect to |

| . This is a free running clock and is synchronized to the input clock | |||

| CQ |

|

| CQ | C | ||||||

|

|

|

|

| for output data (C) of the | ||||||

|

|

|

|

| for the echo clocks are shown in the AC timing table. | ||||||

| ZQ | Input | Output Impedance Matching Input. This input is used to tune the device outputs to the system data bus | ||||||||

|

|

|

|

| impedance. CQ, CQ, and Q[x:0] output impedance are set to 0.2 x RQ, where RQ is a resistor connected | ||||||

|

|

|

|

| between ZQ and ground. Alternatively, this pin can be connected directly to VDDQ, which enables the | ||||||

|

|

|

|

| minimum impedance mode. This pin cannot be connected directly to GND or left unconnected. | ||||||

|

|

|

| Input | DLL Turn Off − Active LOW. Connecting this pin to ground turns off the DLL inside the device. The | ||||||

| DOFF | ||||||||||

|

|

|

|

| timings in the DLL turned off operation differs from those listed in this data sheet. For normal operation, | ||||||

|

|

|

|

| this pin can be connected to a pull up through a 10 KΩ or less pull up resistor. The device behaves in | ||||||

|

|

|

|

| |||||||

|

|

|

|

| to 167 MHz with | ||||||

| TDO | Output | TDO for JTAG. | ||||||||

|

|

|

| ||||||||

| TCK | Input | TCK Pin for JTAG. | ||||||||

|

|

|

| ||||||||

| TDI | Input | TDI Pin for JTAG. | ||||||||

|

|

|

| ||||||||

| TMS | Input | TMS Pin for JTAG. | ||||||||

|

|

|

| ||||||||

| NC | N/A | Not Connected to the Die. Can be tied to any voltage level. | ||||||||

|

|

|

| ||||||||

| NC/72M | N/A | Not Connected to the Die. Can be tied to any voltage level. | ||||||||

|

|

|

| ||||||||

| NC/144M | N/A | Not Connected to the Die. Can be tied to any voltage level. | ||||||||

|

|

|

| ||||||||

| NC/288M | N/A | Not Connected to the Die. Can be tied to any voltage level. | ||||||||

|

|

|

| ||||||||

| VREF | Input- | Reference Voltage Input. Static input used to set the reference level for HSTL inputs, outputs, and AC | ||||||||

|

|

|

| Reference | measurement points. | ||||||

| VDD | Power Supply | Power Supply Inputs to the Core of the Device. | ||||||||

| VSS | Ground | Ground for the Device. | ||||||||

| VDDQ | Power Supply | Power Supply Inputs for the Outputs of the Device. | ||||||||

Document Number: | Page 7 of 30 |

[+] Feedback