ST92195B

■Register File based 8/16 bit Core Architecture with RUN, WFI, SLOW and HALT modes

■0°C to +70°C operating temperature range

■Up to 24 MHz. operation @ 5V±10%

■Min. instruction cycle time: 165ns at 24 MHz.

■32, 48, 56 or 64 Kbytes ROM

■256 bytes RAM of Register file (accumulators or index registers)

■256 bytes of

■2, 6 or 8 Kbytes of TDSRAM (Teletext and Display Storage RAM)

■28 fully programmable I/O pins

■Serial Peripheral Interface

■Flexible Clock controller for OSD, Data Slicer and Core clocks running from a single low frequency external crystal.

■Enhanced display controller with 26 rows of 40/80 characters

–Serial and Parallel attributes

–10x10 dot matrix, 512 ROM characters, defin- able by user

–4/3 and 16/9 supported in 50/60Hz and 100/ 120 Hz mode

–Rounding, fringe, double width, double height, scrolling, cursor, full background color, half- intensity color, translucency and

■Teletext unit, including Data Slicer, Acquisition Unit and up to 8 Kbytes RAM for data storage

■VPS and Wide Screen Signalling slicer (on some devices)

■Integrated Sync Extractor and Sync Controller

■

■Up to 6 external interrupts plus one Non- Maskable Interrupt

■8 x

■

■One

■

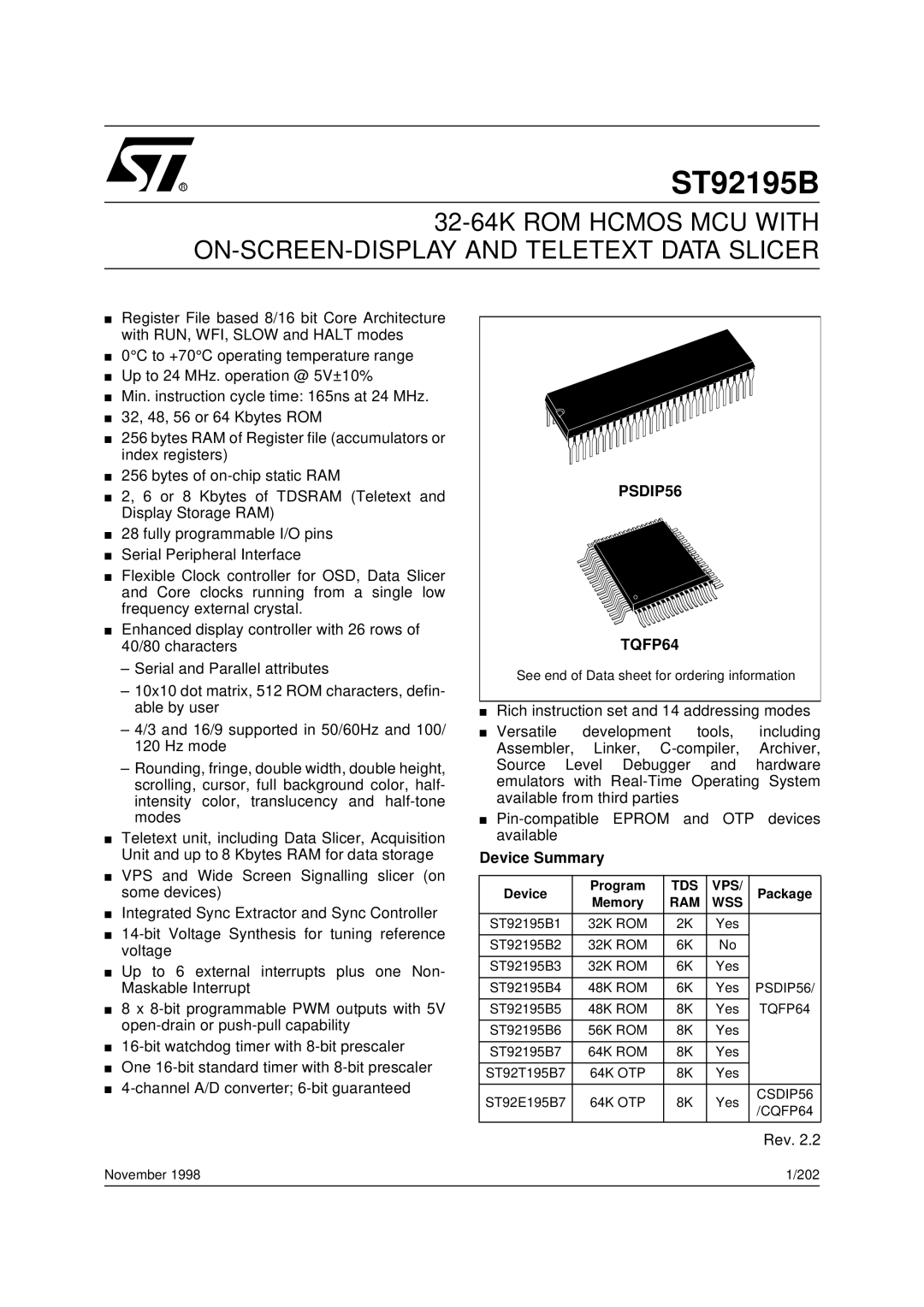

PSDIP56 |

TQFP64 |

See end of Data sheet for ordering information |

■Rich instruction set and 14 addressing modes

■Versatile development tools, including Assembler, Linker,

■

Device Summary

Device | Program | TDS | VPS/ | Package | |

Memory | RAM | WSS | |||

|

| ||||

|

|

|

|

| |

ST92195B1 | 32K ROM | 2K | Yes |

| |

|

|

|

|

| |

ST92195B2 | 32K ROM | 6K | No |

| |

|

|

|

|

| |

ST92195B3 | 32K ROM | 6K | Yes |

| |

|

|

|

|

| |

ST92195B4 | 48K ROM | 6K | Yes | PSDIP56/ | |

|

|

|

|

| |

ST92195B5 | 48K ROM | 8K | Yes | TQFP64 | |

|

|

|

|

| |

ST92195B6 | 56K ROM | 8K | Yes |

| |

|

|

|

|

| |

ST92195B7 | 64K ROM | 8K | Yes |

| |

|

|

|

|

| |

ST92T195B7 | 64K OTP | 8K | Yes |

| |

|

|

|

|

| |

ST92E195B7 | 64K OTP | 8K | Yes | CSDIP56 | |

/CQFP64 | |||||

|

|

|

| ||

|

|

|

|

|

Rev. 2.2

November 1998 | 1/202 |