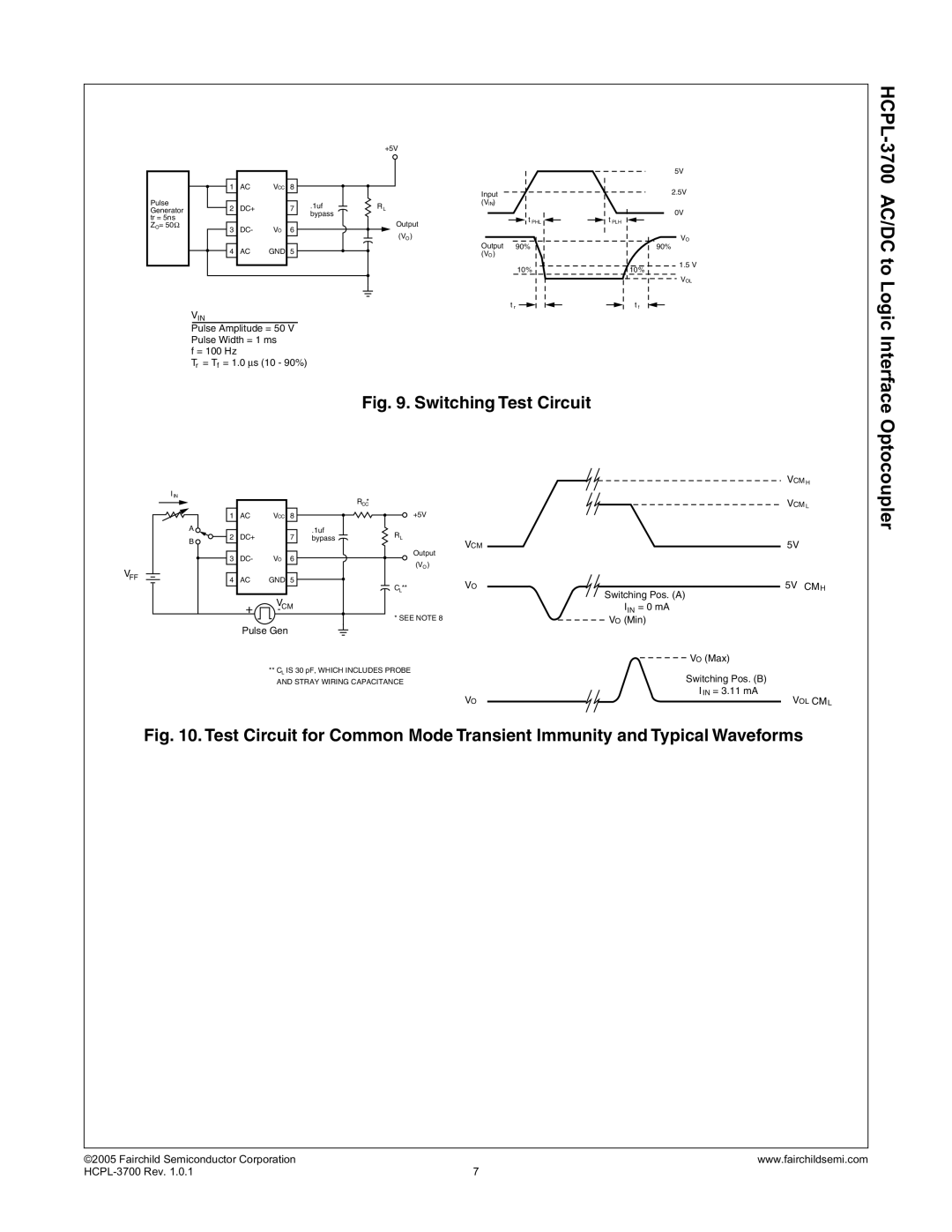

Pulse Generator tr = 5ns ZO= 50Ω

|

| 1 | AC | VCC |

| 8 | .1uf |

|

|

| DC+ |

|

|

| |

|

| 2 |

|

| 7 | ||

|

|

|

| ||||

|

|

|

| bypass | |||

|

|

| DC- | VO |

|

| |

|

|

|

|

| |||

|

|

|

|

|

| ||

|

| 3 |

| 6 |

| ||

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 | AC | GND |

| 5 |

|

|

|

|

+5V

| Input | ||

RL | (VIN) | ||

|

|

| |

Output |

|

| t PHL |

|

| ||

|

|

| |

(VO )

Output 90% (VO )

5V

2.5V

0V

t PLH

VO

90%

HCPL-3700 AC/DC

VIN

10%

t r

10%

t f

1.5 V

VOL

to Logic

IIN

VFF

Pulse Amplitude = 50 V Pulse Width = 1 ms

f = 100 Hz

Tr = Tf = 1.0 ∝s (10 - 90%)

Fig. 9. Switching Test Circuit

|

|

|

|

|

|

| RCC* |

|

| 1 | AC |

| VCC | 8 |

| +5V |

|

A | 2 | DC+ |

|

| 7 | .1uf | RL |

|

B |

|

| bypass | VCM | ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| Output | |

| 3 | DC- |

| VO | 6 |

|

| |

|

|

| (VO ) |

| ||||

|

|

|

|

|

|

|

| |

| 4 | AC | GND | 5 |

| CL** | VO | |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

|

| + |

| V |

|

|

|

|

|

|

|

| * SEE NOTE 8 |

| |||

|

|

|

|

|

|

|

| |

Pulse Gen

**CL IS 30 pF, WHICH INCLUDES PROBE AND STRAY WIRING CAPACITANCE

VO

VCM H

VCM L

5V

5V CMH

Switching Pos. (A)

IIN = 0 mA

VO (Min)

VO (Max)

Switching Pos. (B)

IIN = 3.11 mA

VOL CML

Interface Optocoupler

Fig. 10. Test Circuit for Common Mode Transient Immunity and Typical Waveforms

©2005 Fairchild Semiconductor Corporation | www.fairchildsemi.com |

7 |