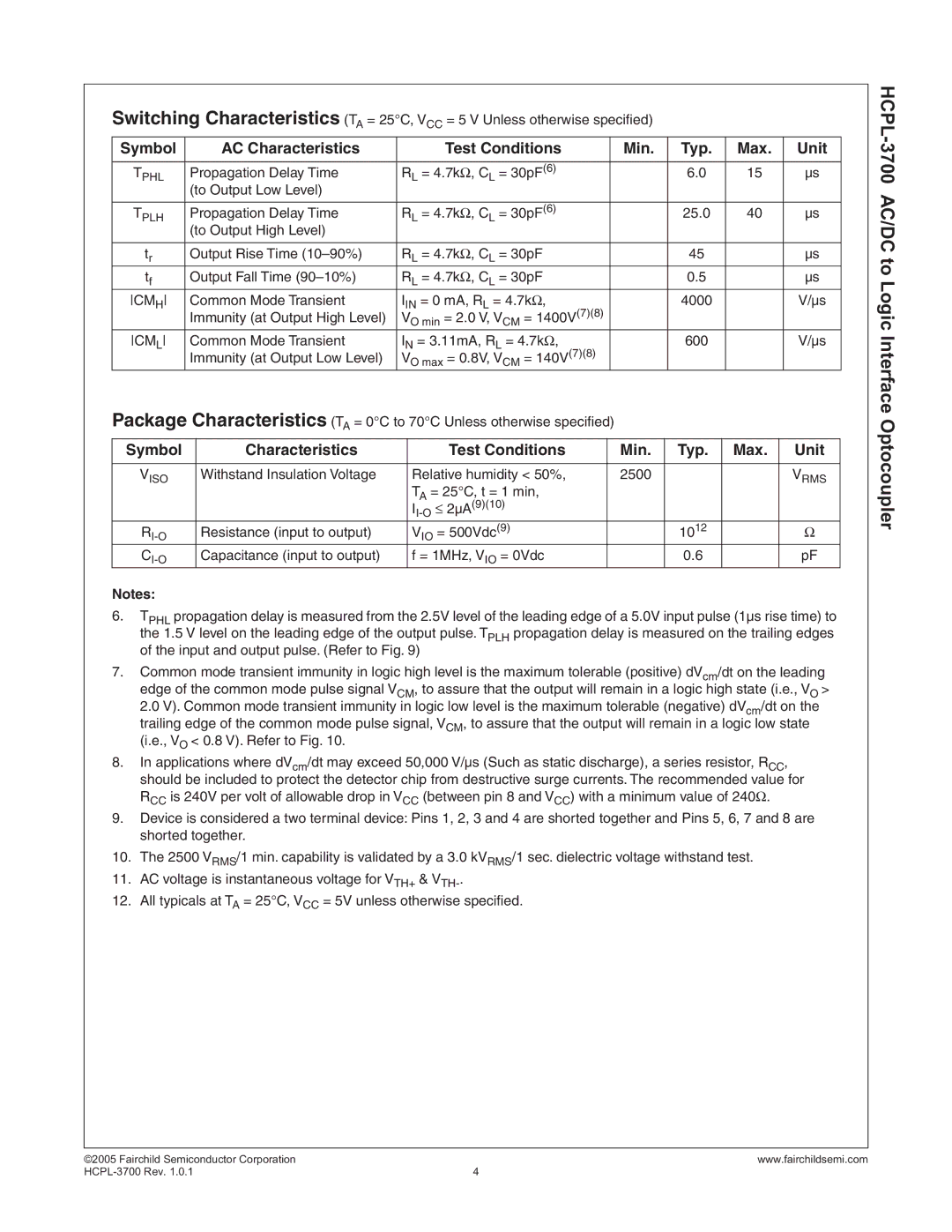

Switching Characteristics (TA = 25°C, VCC = 5 V Unless otherwise specified)

Symbol | AC Characteristics |

| Test Conditions | Min. | Typ. | Max. | Unit |

|

|

|

|

|

|

| |

TPHL | Propagation Delay Time | RL = 4.7kΩ, CL = 30pF(6) |

| 6.0 | 15 | µs | |

| (to Output Low Level) |

|

|

|

|

|

|

|

|

|

|

|

|

| |

TPLH | Propagation Delay Time | RL = 4.7kΩ, CL = 30pF(6) |

| 25.0 | 40 | µs | |

| (to Output High Level) |

|

|

|

|

|

|

|

|

|

|

|

|

| |

tr | Output Rise Time | RL = 4.7kΩ, CL = 30pF |

| 45 |

| µs | |

tf | Output Fall Time | RL = 4.7kΩ, CL = 30pF |

| 0.5 |

| µs | |

CMH | Common Mode Transient | IIN = 0 mA, RL = 4.7kΩ, |

| 4000 |

| V/µs | |

| Immunity (at Output High Level) | V | = 2.0 V, V = 1400V(7)(8) |

|

|

|

|

|

| O min | CM |

|

|

|

|

CML | Common Mode Transient | IN = 3.11mA, RL = 4.7kΩ, |

| 600 |

| V/µs | |

| Immunity (at Output Low Level) | VO max = 0.8V, VCM = 140V(7)(8) |

|

|

|

| |

Package Characteristics (TA = 0°C to 70°C Unless otherwise specified)

Symbol | Characteristics | Test Conditions | Min. | Typ. | Max. | Unit | |

|

|

|

|

|

|

| |

VISO | Withstand Insulation Voltage | Relative humidity < 50%, | 2500 |

|

| VRMS | |

|

|

| TA = 25°C, t = 1 min, |

|

|

|

|

|

|

|

|

|

|

| |

R | Resistance (input to output) | V = 500Vdc(9) |

| 1012 |

| Ω | |

|

| IO |

|

|

|

| |

Capacitance (input to output) | f = 1MHz, VIO = 0Vdc |

| 0.6 |

| pF | ||

Notes:

6.TPHL propagation delay is measured from the 2.5V level of the leading edge of a 5.0V input pulse (1µs rise time) to the 1.5 V level on the leading edge of the output pulse. TPLH propagation delay is measured on the trailing edges of the input and output pulse. (Refer to Fig. 9)

7.Common mode transient immunity in logic high level is the maximum tolerable (positive) dVcm/dt on the leading edge of the common mode pulse signal VCM, to assure that the output will remain in a logic high state (i.e., VO > 2.0 V). Common mode transient immunity in logic low level is the maximum tolerable (negative) dVcm/dt on the trailing edge of the common mode pulse signal, VCM, to assure that the output will remain in a logic low state (i.e., VO < 0.8 V). Refer to Fig. 10.

8.In applications where dVcm/dt may exceed 50,000 V/µs (Such as static discharge), a series resistor, RCC, should be included to protect the detector chip from destructive surge currents. The recommended value for RCC is 240V per volt of allowable drop in VCC (between pin 8 and VCC) with a minimum value of 240Ω.

9.Device is considered a two terminal device: Pins 1, 2, 3 and 4 are shorted together and Pins 5, 6, 7 and 8 are shorted together.

10.The 2500 VRMS/1 min. capability is validated by a 3.0 kVRMS/1 sec. dielectric voltage withstand test.

11.AC voltage is instantaneous voltage for VTH+ &

12.All typicals at TA = 25°C, VCC = 5V unless otherwise specified.

HCPL-3700 AC/DC to Logic Interface Optocoupler

©2005 Fairchild Semiconductor Corporation | www.fairchildsemi.com |

4 |