plane. In most circumstances, however, it is prudent to place a filter circuit on AVDD; refer to the CPC710 DD3.x User’s Manual for more information.

ØThe PLL is now set up and controlled by external signals PLL_RANGE [1:0] and 6 external signals PLL_TUNE [5:0] instead of PLL133 and PLL_TUNE [1:0]. This is a change from the previous revision.

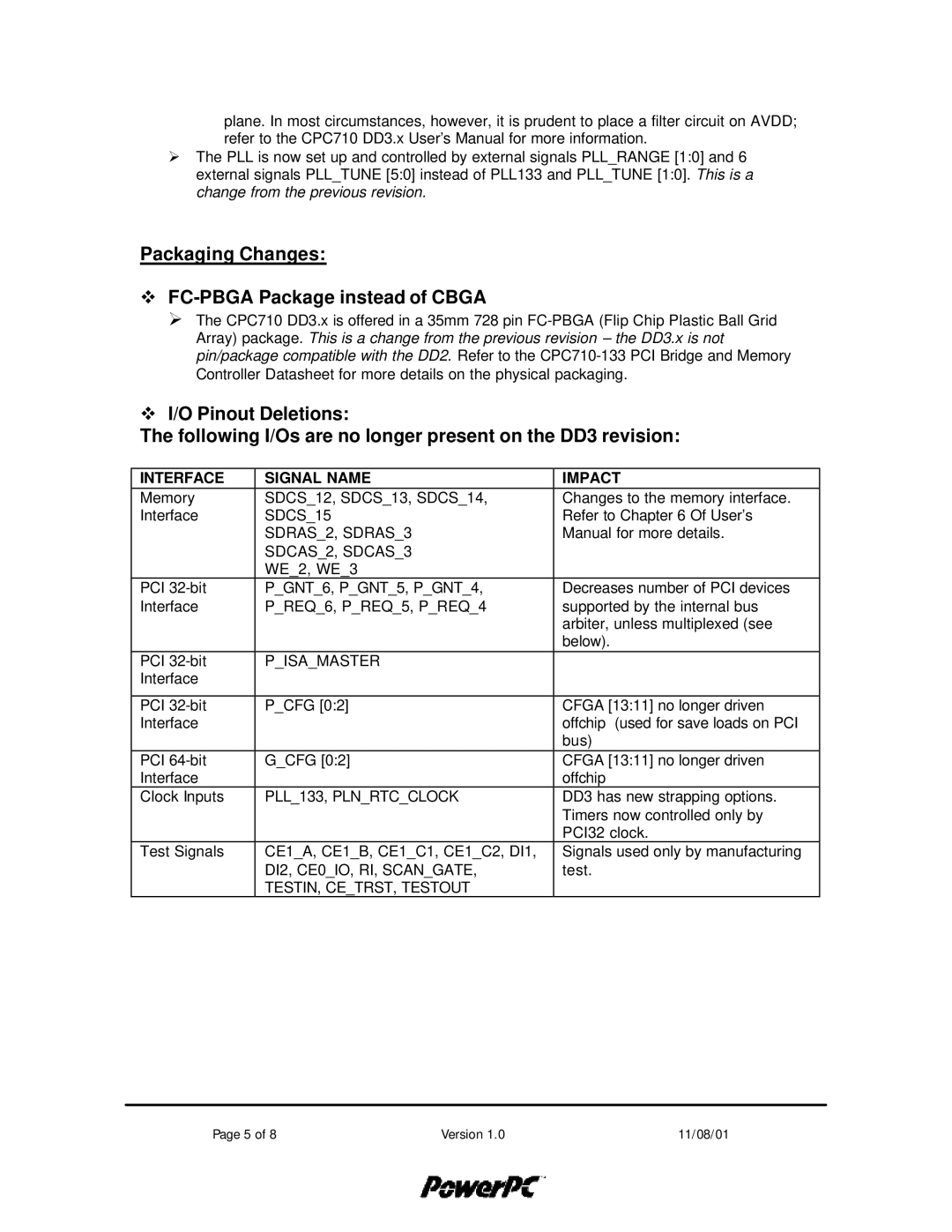

Packaging Changes:

vFC-PBGA Package instead of CBGA

ØThe CPC710 DD3.x is offered in a 35mm 728 pin

vI/O Pinout Deletions:

The following I/Os are no longer present on the DD3 revision:

INTERFACE | SIGNAL NAME | IMPACT |

Memory | SDCS_12, SDCS_13, SDCS_14, | Changes to the memory interface. |

Interface | SDCS_15 | Refer to Chapter 6 Of User’s |

| SDRAS_2, SDRAS_3 | Manual for more details. |

| SDCAS_2, SDCAS_3 |

|

| WE_2, WE_3 |

|

PCI | P_GNT_6, P_GNT_5, P_GNT_4, | Decreases number of PCI devices |

Interface | P_REQ_6, P_REQ_5, P_REQ_4 | supported by the internal bus |

|

| arbiter, unless multiplexed (see |

|

| below). |

PCI | P_ISA_MASTER |

|

Interface |

|

|

|

|

|

PCI | P_CFG [0:2] | CFGA [13:11] no longer driven |

Interface |

| offchip (used for save loads on PCI |

|

| bus) |

PCI | G_CFG [0:2] | CFGA [13:11] no longer driven |

Interface |

| offchip |

Clock Inputs | PLL_133, PLN_RTC_CLOCK | DD3 has new strapping options. |

|

| Timers now controlled only by |

|

| PCI32 clock. |

Test Signals | CE1_A, CE1_B, CE1_C1, CE1_C2, DI1, | Signals used only by manufacturing |

| DI2, CE0_IO, RI, SCAN_GATE, | test. |

| TESTIN, CE_TRST, TESTOUT |

|

Page 5 of 8 | Version 1.0 | 11/08/01 |