Developer Manual

RN3 | 10 | |

CM1 | ||

9 | ||

R8 | ||

8 | ||

R7 | ||

7 | ||

R6 | ||

6 | ||

R5 | ||

5 | ||

CM2 | ||

4 | ||

R4 | ||

3 | ||

R3 | ||

2 | ||

R2 | ||

1 | ||

R1 | ||

| ||

|

|

R.NETWORK 100K

| JP1 |

|

TCLK0 | 1 | 2 |

3 | 4 | |

TPOS0/TDATA0 | 5 | 6 |

TNEG0/UBS0 | 7 | 8 |

LOS0 | 9 | 10 |

| HEADER 5X2 | |

TCLK0 |

|

|

TCLK1 |

|

|

TCLK2 |

|

|

TCLK3 |

|

|

TCLK4 |

|

|

TCLK5 | JP3 |

|

TCLK6 | 1 | 2 |

TCLK7 | ||

TCLK1 | 3 | 4 |

TPOS1/TDATA1 | 5 | 6 |

TNEG1/UBS1 | 7 | 8 |

LOS1 | 9 | 10 |

RCLK0

RPOS0/RDATA0

RNEG0/BPV0

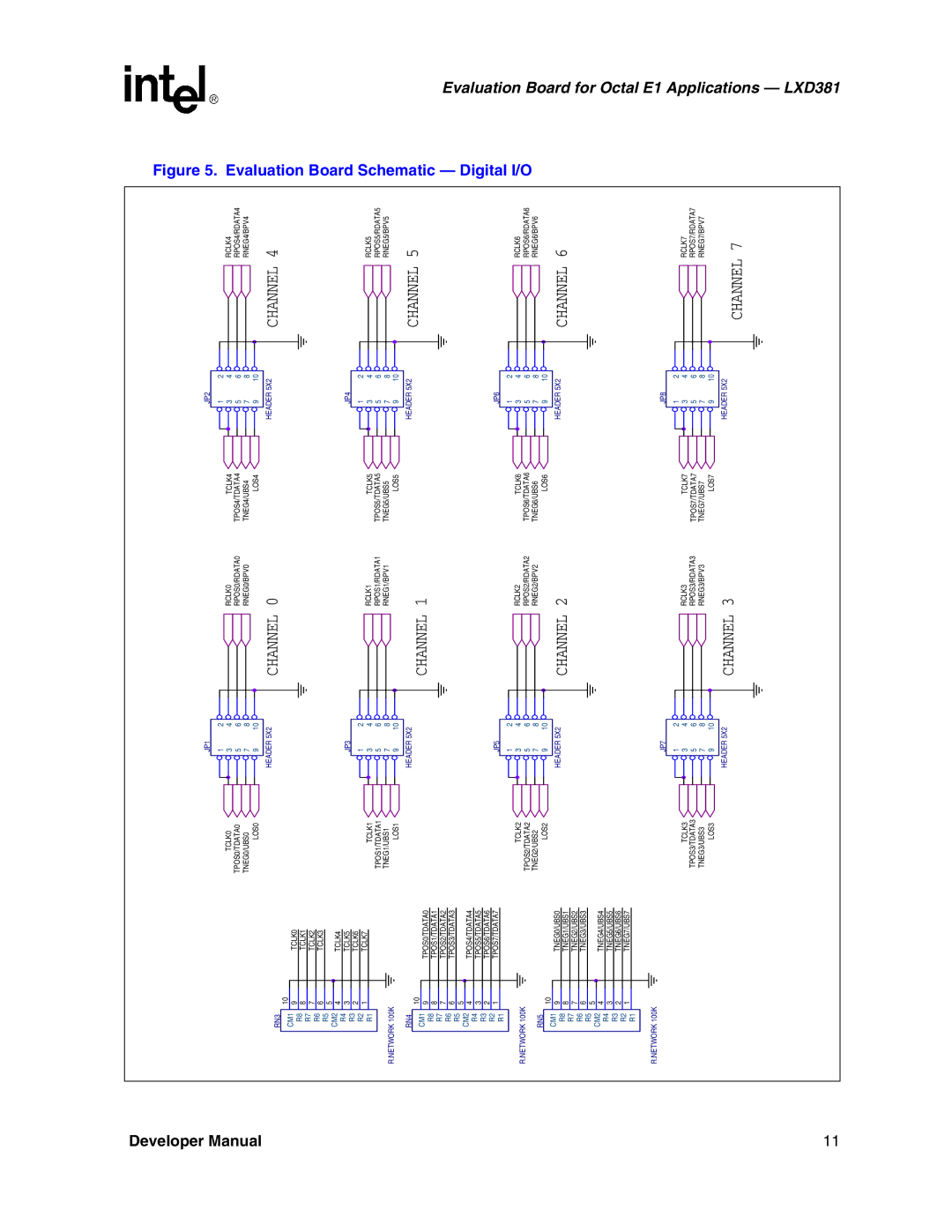

CHANNEL 0

RCLK1

RPOS1/RDATA1

RNEG1/BPV1

TCLK4

TPOS4/TDATA4

TNEG4/UBS4

LOS4

TCLK5

TPOS5/TDATA5

TNEG5/UBS5

LOS5

JP2

1 | 2 |

3 | 4 |

5 | 6 |

78

910

HEADER 5X2

JP4

1 | 2 |

3 | 4 |

5 | 6 |

78

910

RCLK4

RPOS4/RDATA4

RNEG4/BPV4

CHANNEL 4

RCLK5

RPOS5/RDATA5

RNEG5/BPV5

Figure 5. |

Evaluation Board Schematic |

RN4 | 10 | |

CM1 | ||

9 | ||

R8 | ||

8 | ||

R7 | ||

7 | ||

R6 | ||

6 | ||

R5 | ||

5 | ||

CM2 | ||

4 | ||

R4 | ||

3 | ||

R3 | ||

2 | ||

R2 | ||

1 | ||

R1 | ||

|

R.NETWORK 100K

RN5 |

10 |

CM1 |

| HEADER 5X2 | |

TPOS0/TDATA0 |

|

|

TPOS1/TDATA1 |

|

|

TPOS2/TDATA2 |

|

|

TPOS3/TDATA3 |

|

|

TPOS4/TDATA4 |

|

|

TPOS5/TDATA5 |

|

|

TPOS6/TDATA6 |

|

|

TPOS7/TDATA7 | JP5 |

|

TCLK2 | 1 | 2 |

3 | 4 | |

TPOS2/TDATA2 | 5 | 6 |

TNEG2/UBS2 | 7 | 8 |

LOS2 | 9 | 10 |

CHANNEL 1

RCLK2

RPOS2/RDATA2

RNEG2/BPV2

HEADER 5X2

| JP6 |

|

TCLK6 | 1 | 2 |

3 | 4 | |

TPOS6/TDATA6 | 5 | 6 |

TNEG6/UBS6 | 7 | 8 |

LOS6 | 9 | 10 |

CHANNEL 5

RCLK6

RPOS6/RDATA6

RNEG6/BPV6

— Digital I/O | Evaluation Board |

11

|

| |

R8 | 9 | |

8 | ||

R7 | ||

7 | ||

R6 | ||

6 | ||

R5 | ||

5 | ||

CM2 | ||

4 | ||

R4 | ||

3 | ||

R3 | ||

2 | ||

R2 | ||

1 | ||

R1 | ||

| ||

|

|

R.NETWORK 100K

TNEG0/UBS0 | HEADER 5X2 | |

TNEG1/UBS1 |

|

|

TNEG2/UBS2 |

|

|

TNEG3/UBS3 |

|

|

TNEG4/UBS4 |

|

|

TNEG5/UBS5 |

|

|

TNEG6/UBS6 |

|

|

TNEG7/UBS7 |

|

|

| JP7 |

|

TCLK3 | 1 | 2 |

3 | 4 | |

TPOS3/TDATA3 | 5 | 6 |

TNEG3/UBS3 | 7 | 8 |

LOS3 | 9 | 10 |

HEADER 5X2

CHANNEL 2

RCLK3

RPOS3/RDATA3

RNEG3/BPV3

CHANNEL 3

TCLK7

TPOS7/TDATA7

TNEG7/UBS7

LOS7

HEADER 5X2

JP8

1 | 2 |

3 | 4 |

5 | 6 |

78

910

HEADER 5X2

CHANNEL 6

RCLK7

RPOS7/RDATA7

RNEG7/BPV7

CHANNEL 7

for Octal E1 Applications — LXD381 |