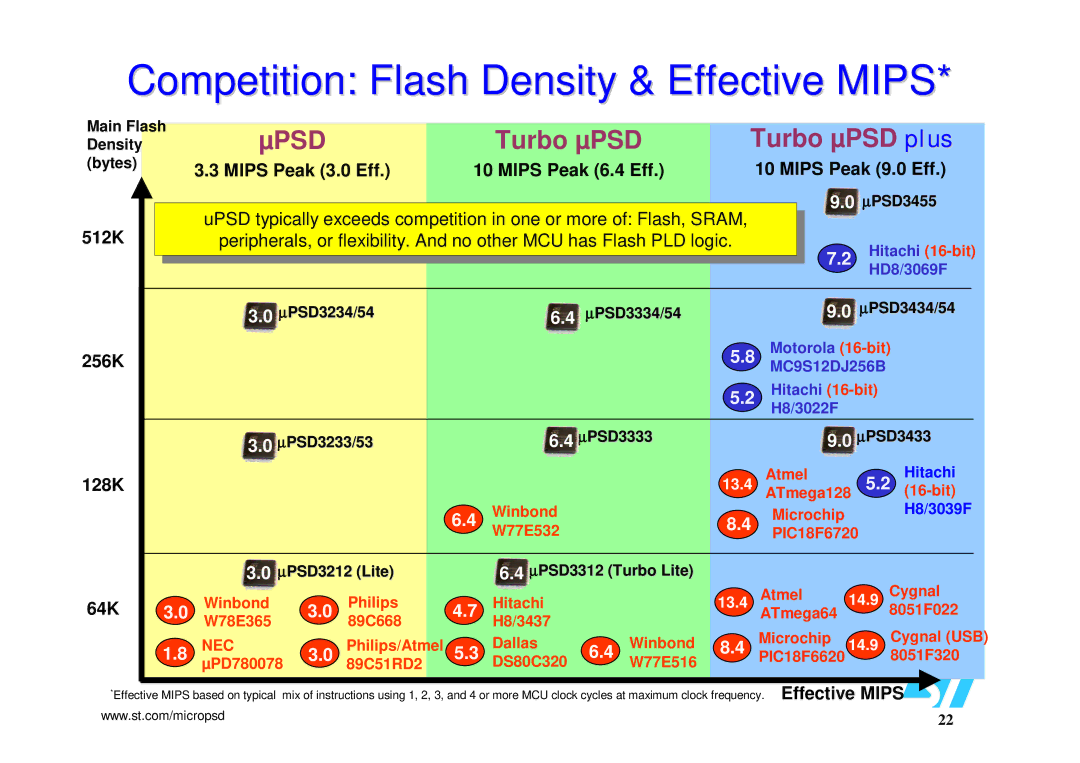

Competition: Flash Density & Effectiveive MIPS*MIPS*

Main Flash | µPSD | Turbo µPSD | Turbo µPSD plusplus |

Density | |||

(bytes) | 3.3 MIPS Peak (3.0 Eff.) | 10 MIPS Peak (6.4 Eff.) | 10 MIPS Peak (9.0 Eff.) |

|

| uPSD typically exceeds competition in one or more of: Flash, SRAM, |

| 9.0 | ∝ PSD3455PSD3455 | |||||||||

|

|

|

|

|

|

| ||||||||

512K |

| uPSD typically exceeds competition in one or more of: Flash, SRAM, |

|

|

|

|

| |||||||

| peripherals, or flexibility. And no other MCU has Flash PLD logic. |

| 7.2 | Hitachi | ||||||||||

|

| peripherals, or flexibility. And no other MCU has Flash PLD logic. |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| HD8/3069F | |

|

| 3.0 ∝ | PSD3234/54 |

| 6.4 ∝ PSD3334/54 |

|

| 9.0 ∝ PSD3434/54PSD3434/54 | ||||||

256K |

|

|

|

|

|

|

|

| 5.8 |

| Motorola | |||

|

|

|

|

|

|

|

|

| MC9S12DJ256B |

| ||||

|

|

|

|

|

|

|

|

| 5.2 |

| Hitachi |

| ||

|

|

|

|

|

|

|

|

|

|

| H8/3022F |

|

|

|

|

| 3.0 ∝ | PSD3233/53 |

| 6.4 ∝ PSD3333 |

|

| 9.0 ∝ | PSD3433PSD3433 | |||||

128K |

|

|

|

|

|

|

|

| 13.4 |

| Atmel |

| 5.2 Hitachi | |

|

|

|

|

|

|

|

|

|

|

| ATmega128 |

| ||

|

|

|

|

| 6.4 | Winbond |

|

| 8.4 |

| Microchip |

|

| H8/3039F |

|

|

|

|

| W77E532 |

|

|

| PIC18F6720 |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| 3.0 ∝ | PSD3212 (Lite) |

| 6.4 ∝ PSD3312 (Turbo Lite) |

| Atmel |

|

| Cygnal | ||||

64K |

| W78E365Winbond | 3.0 | 89C668Philips | 4.7 | H8/3437Hitachi |

|

| 13.4 | 14.9 | ||||

3.0 |

|

| ATmega64 | 8051F022 | ||||||||||

| 1.8 | µPD780078NEC | 3.0 | 89C51RD2Philips/Atmel | 5.3 | DS80C320Dallas | 6.4 | W77E516Winbond | 8.4 | PIC18F6620Microchip | 14.9 | Cygnal (USB) | ||

| 8051F320 | |||||||||||||

*Effective MIPS based on typical mix of instructions using 1, 2, 3, and 4 or more MCU clock cycles at maximum clock frequency. | Effective MIPS | |||||||||||||

www.st.com/micropsd |

|

|

|

|

|

|

|

|

|

|

| 22 | ||