|

| Specifications | ||||

|

|

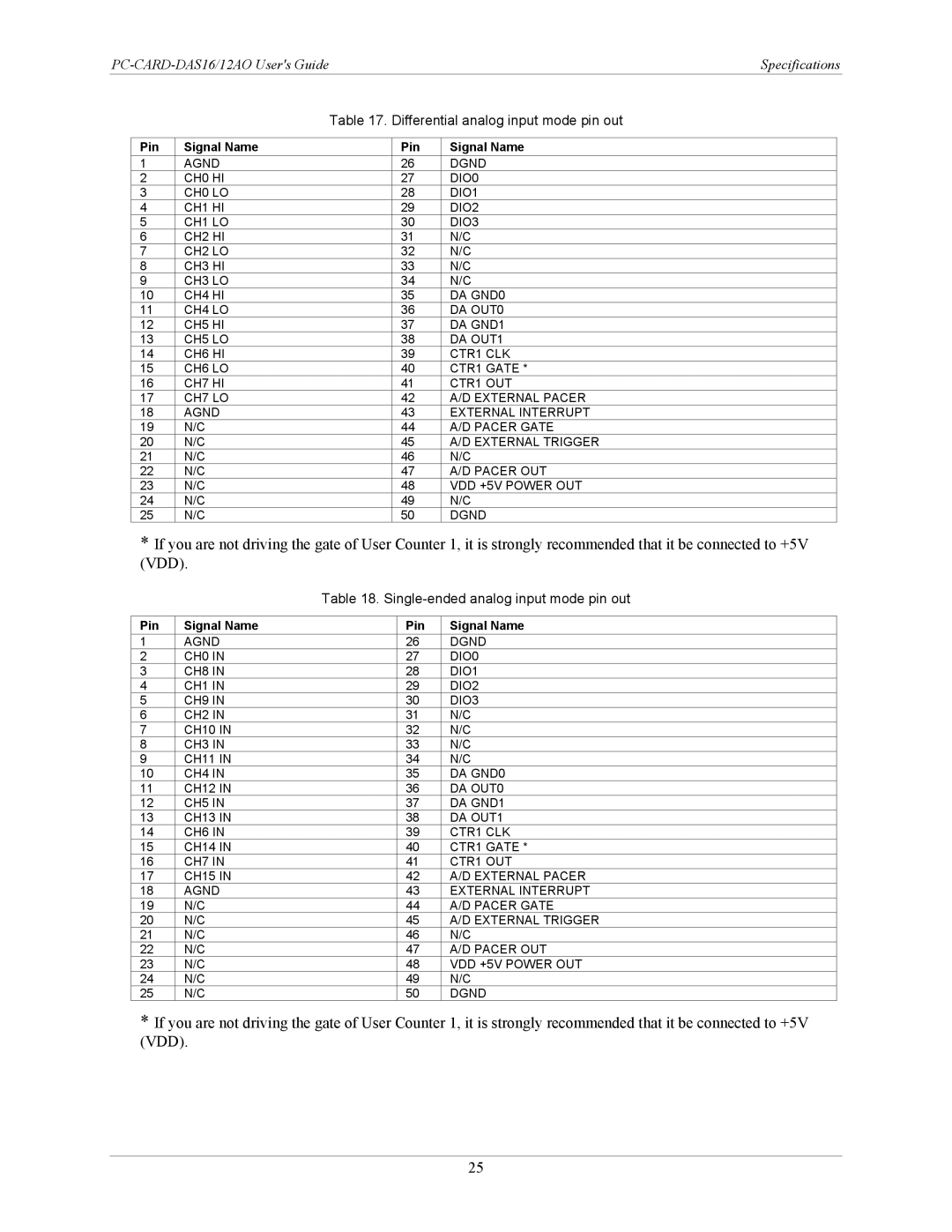

| Table 17. Differential analog input mode pin out | |||

|

|

|

|

|

|

|

| Pin | Signal Name |

| Pin | Signal Name |

|

| 1 | AGND |

| 26 | DGND |

|

| 2 | CH0 HI |

| 27 | DIO0 |

|

| 3 | CH0 LO |

| 28 | DIO1 |

|

| 4 | CH1 HI |

| 29 | DIO2 |

|

| 5 | CH1 LO |

| 30 | DIO3 |

|

| 6 | CH2 HI |

| 31 | N/C |

|

| 7 | CH2 LO |

| 32 | N/C |

|

| 8 | CH3 HI |

| 33 | N/C |

|

| 9 | CH3 LO |

| 34 | N/C |

|

| 10 | CH4 HI |

| 35 | DA GND0 |

|

| 11 | CH4 LO |

| 36 | DA OUT0 |

|

| 12 | CH5 HI |

| 37 | DA GND1 |

|

| 13 | CH5 LO |

| 38 | DA OUT1 |

|

| 14 | CH6 HI |

| 39 | CTR1 CLK |

|

| 15 | CH6 LO |

| 40 | CTR1 GATE * |

|

| 16 | CH7 HI |

| 41 | CTR1 OUT |

|

| 17 | CH7 LO |

| 42 | A/D EXTERNAL PACER |

|

| 18 | AGND |

| 43 | EXTERNAL INTERRUPT |

|

| 19 | N/C |

| 44 | A/D PACER GATE |

|

| 20 | N/C |

| 45 | A/D EXTERNAL TRIGGER |

|

| 21 | N/C |

| 46 | N/C |

|

| 22 | N/C |

| 47 | A/D PACER OUT |

|

| 23 | N/C |

| 48 | VDD +5V POWER OUT |

|

| 24 | N/C |

| 49 | N/C |

|

| 25 | N/C |

| 50 | DGND |

|

*If you are not driving the gate of User Counter 1, it is strongly recommended that it be connected to +5V (VDD).

Table 18. Single-ended analog input mode pin out

Pin | Signal Name | Pin | Signal Name |

1 | AGND | 26 | DGND |

2 | CH0 IN | 27 | DIO0 |

3 | CH8 IN | 28 | DIO1 |

4 | CH1 IN | 29 | DIO2 |

5 | CH9 IN | 30 | DIO3 |

6 | CH2 IN | 31 | N/C |

7 | CH10 IN | 32 | N/C |

8 | CH3 IN | 33 | N/C |

9 | CH11 IN | 34 | N/C |

10 | CH4 IN | 35 | DA GND0 |

11 | CH12 IN | 36 | DA OUT0 |

12 | CH5 IN | 37 | DA GND1 |

13 | CH13 IN | 38 | DA OUT1 |

14 | CH6 IN | 39 | CTR1 CLK |

15 | CH14 IN | 40 | CTR1 GATE * |

16 | CH7 IN | 41 | CTR1 OUT |

17 | CH15 IN | 42 | A/D EXTERNAL PACER |

18 | AGND | 43 | EXTERNAL INTERRUPT |

19 | N/C | 44 | A/D PACER GATE |

20 | N/C | 45 | A/D EXTERNAL TRIGGER |

21 | N/C | 46 | N/C |

22 | N/C | 47 | A/D PACER OUT |

23 | N/C | 48 | VDD +5V POWER OUT |

24 | N/C | 49 | N/C |

25 | N/C | 50 | DGND |

*If you are not driving the gate of User Counter 1, it is strongly recommended that it be connected to +5V (VDD).

25