Functional Details |

Control Register BASE + 6h

TRGPOL TRGSEL | TRGCLR | CLK2 | CTR1 |

|

| 10K |

| 5 | 39 | CRT1 CLK |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| 5 | 10K | 40 |

|

|

|

|

|

|

|

|

| CTR1 GATE | ||

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

| GATE |

| OUT |

|

|

|

|

|

|

|

| Counter 1 |

| 41 | CTR1 OUT | |

| 1/10 |

|

|

|

|

|

| |||

|

|

|

|

| CLK |

|

|

|

| |

| 1/10 | 0 |

|

|

| CLK |

| OUT |

|

|

| 1 |

|

|

| Counter 2 |

|

|

|

| |

|

|

|

|

| GATE |

|

|

|

| |

| 10 MHz |

|

|

|

| CLK |

| OUT | 47 | A/D INTERNAL |

| OSC |

|

|

|

| Counter 3 |

|

| PACER OUT | |

|

|

|

|

|

| GATE |

|

|

|

|

| Trigger |

|

|

|

|

|

|

| 44 | A/D PACER GATE |

| Logic |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| 45 | A/D EXTERNAL |

|

|

|

|

|

|

|

|

| TRIGGER | |

|

|

|

|

|

|

|

|

|

| |

|

|

| TS1 | TS0 | Control register |

|

|

|

| |

|

|

|

|

|

| BASE + 4h |

|

|

|

|

| A/D Convert CLock | 1 | 0 | 3 |

|

|

|

|

| |

| MUX | 2 | Trigger |

|

|

| A/D EXTERNAL | |||

|

|

| 1 |

|

| 42 | ||||

|

|

|

|

| Logic |

|

| CLOCK | ||

|

|

|

|

| 0 |

|

|

| ||

|

|

|

|

| S/W CONVERT |

|

|

|

| |

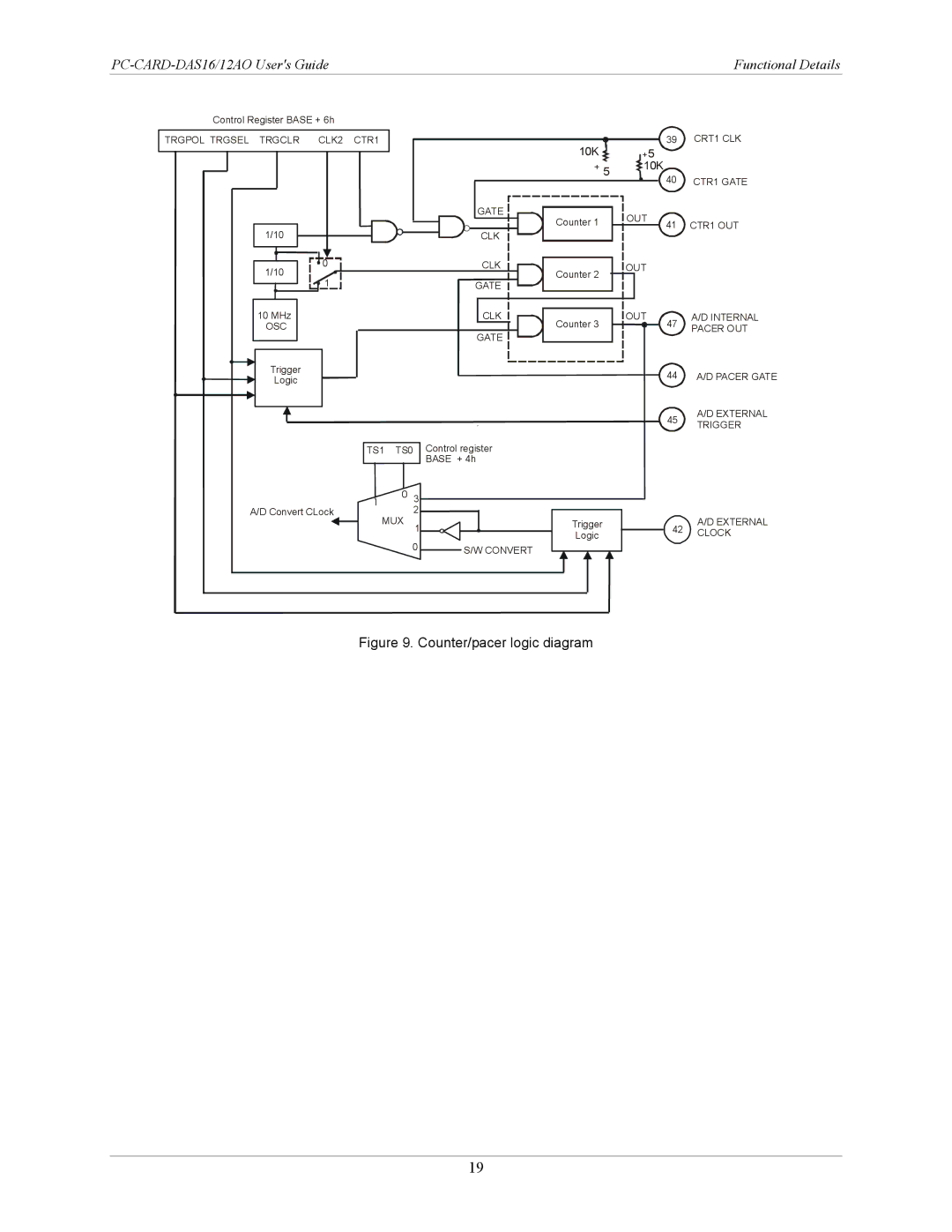

Figure 9. Counter/pacer logic diagram

19