Compiler Support on StarCore

The following instructions bring more than one byte at a time to the data register:

move.w (Rx), Dn move.f (Rx), Dn move.2w (Rx), Dh move.2f (Rx), Dh move.4w (Rx), Dk move.4f (Rx), Dk move.2l (Rx), Dh

Transfer one

where x spans from 0 to 15 and the data register notations are as follows:

•Dn represents D0, D1, D2, D3, D4, D5, D6, D7, D8, D9, D10, D11, D12, D13, D14, or D15.

•Dh represents D0:D1, D2:D3, D4:D5, D6:D7, D8:D9, D10:D11, D12:D13, or D14:D15.

•Dk represents D0:D1:D2:D3, D4:D5:D6:D7, D8:D9:D10:D11, or D12:D13:D14:D15.

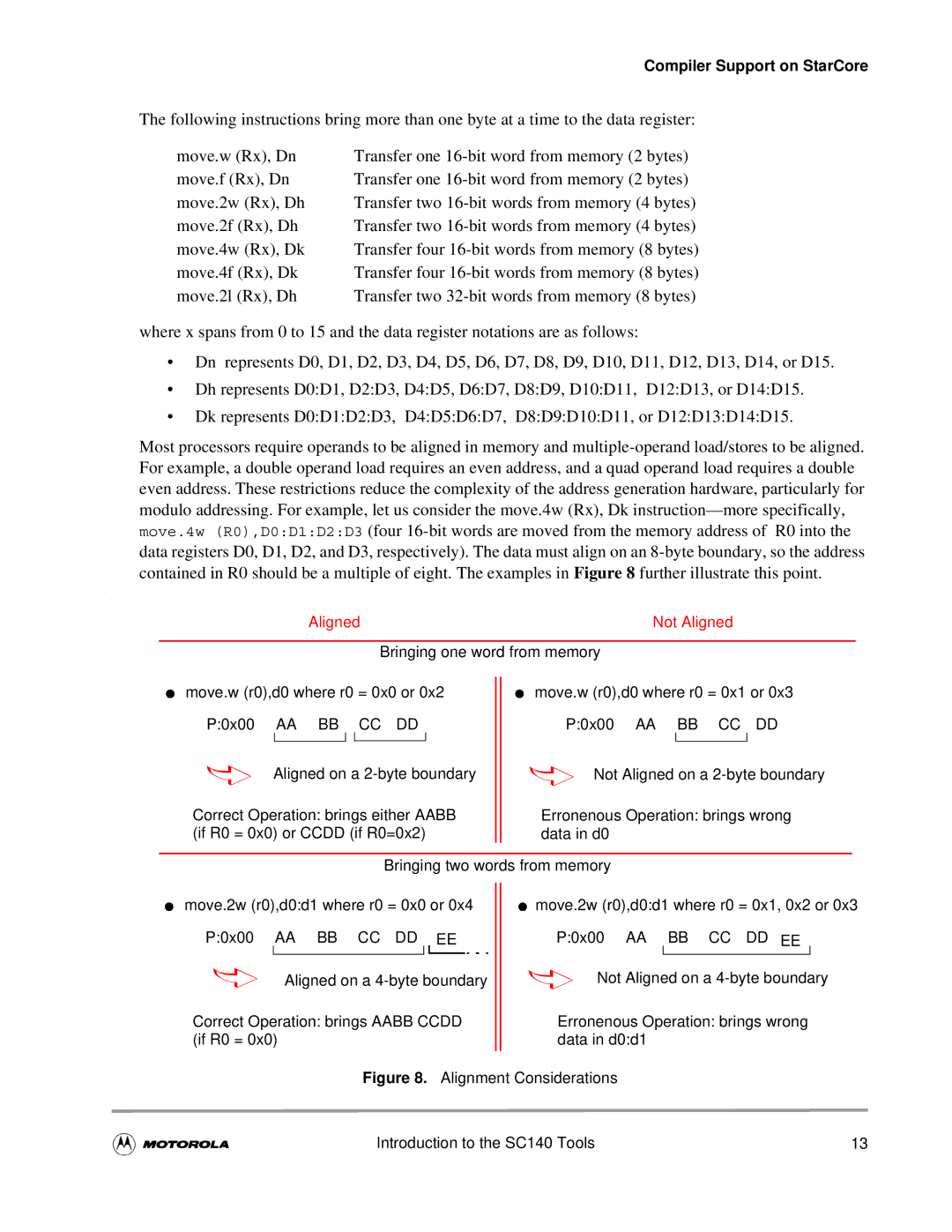

Most processors require operands to be aligned in memory and

.

|

|

|

|

|

|

|

|

| Aligned |

|

|

|

|

|

|

|

|

| Not Aligned |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| Bringing one word from memory |

|

|

|

|

|

|

|

|

|

| |||||||||||

move.w (r0),d0 where r0 = 0x0 or 0x2 |

| move.w (r0),d0 where r0 = 0x1 or 0x3 | ||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||

P:0x00 AA BB CC DD |

|

|

|

|

|

|

|

| P:0x00 | AA |

|

| BB | CC | DD | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

| Aligned on a |

|

|

|

|

| Not Aligned on a | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

Correct Operation: brings either AABB |

| Erronenous Operation: brings wrong | ||||||||||||||||||||||||||||||

(if R0 = 0x0) or CCDD (if R0=0x2) |

|

|

|

| data in d0 |

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| Bringing two words from memory |

|

|

|

|

|

|

|

|

|

| |||||||||||

move.2w (r0),d0:d1 where r0 = 0x0 or 0x4 |

| move.2w (r0),d0:d1 where r0 = 0x1, 0x2 or 0x3 | ||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||

P:0x00 |

| AA BB CC DD |

|

|

| EE |

|

|

|

|

|

| P:0x00 | AA |

| BB | CC | DD EE |

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| Aligned on a |

|

|

|

|

| Not Aligned on a | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

Correct Operation: brings AABB CCDD |

|

|

|

|

| Erronenous Operation: brings wrong | ||||||||||||||||||||||||||

(if R0 = 0x0) |

|

|

|

|

|

|

|

| data in d0:d1 |

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

| Figure 8. |

| Alignment Considerations |

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

| Introduction to the SC140 Tools |

|

|

|

|

| 13 | |||||||||||||||